在Xilinx 7系列FPGA使用之CLB探索中研究了CLB的结构,并主要讲述了SLICEM扩展移位寄存器的使用。另外SLICEM还可扩展成分布式RAM,此处就补上对分布式RAM使用的说明。

首先概括一下1个SLICEM可扩展的分布式RAM的所有形式:

• Single-Port 32 x 1-bit RAM

• Dual-Port 32 x 1-bit RAM

• Quad-Port 32 x 2-bit RAM

• Simple Dual-Port 32 x 6-bit RAM

• Single-Port 64 x 1-bit RAM

• Dual-Port 64 x 1-bit RAM

• Quad-Port 64 x 1-bit RAM

• Simple Dual-Port 64 x 3-bit RAM

• Single-Port 128 x 1-bit RAM

• Dual-Port 128 x 1-bit RAM

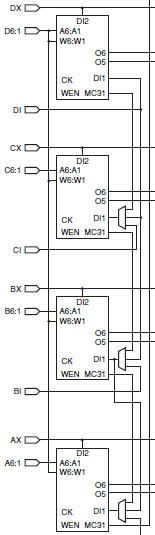

与移位寄存器扩展类似,分布式RAM也是以LUT作为其存储单元,如图1所示为SLICEM中的4个LUT,每个LUT都有如下几个端口:

地址输入:A6:A1 W6:W1

数据输入:DI1 DI2

时钟输入:CK

写使能 :WEN

数据输出:O6 O5

移位输出:MC31 (在此处不使用)

图1

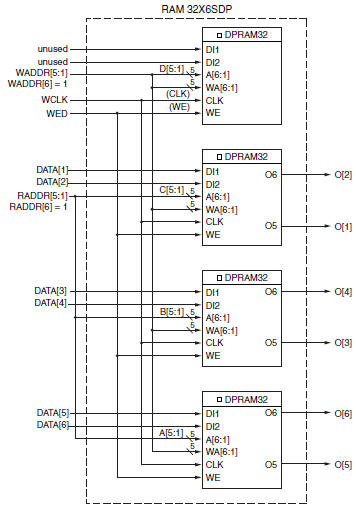

仔细研究可发现,D LUT和A、B、C LUT有所区别,其地址输入都由D6:1驱动,而其它LUT的地址输入除了W6:1统一由D6:1驱动,A6:1分别由A6:1、B6:1、C6:1驱动,因此D LUT只能作为单端口RAM使用,而A、B、C LUT除了能作为单端口RAM使用之外,还能作为双端口RAM。如图2所示,以Simple Dual-Port 32 x 6-bit RAM为例,深度为32-bit,每个LUT都有6输入,将地址最高位置1,使两个输出O6、O5有效,剩下5根地址线可得到32-bit深度;数据宽度6-bit,由A、B、C LUT 的2*3个输出组成。

图2

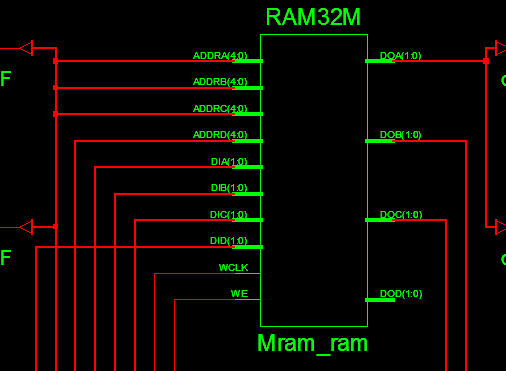

与移位寄存器类似,XST综合器能自动将规范的代码综合成分布式RAM,如以下代码,实现了Simple Dual-Port 32 x 6-bit RAM的结构,综合出的结构如图3所示

module dbram_lab(

input clk,

input rst,

input wen,

input [4:0] raddr,

input [4:0] waddr,

input [5:0] din,

output [5:0] qout

);

reg [5:0] ram[0:31];

always@(posedge clk)

if(wen)

ram[waddr]<=din;

assign qout=ram[raddr];

endmodule

图3

图3中根据代码综合得到的结构基本与图2的理论图一致,其中编写代码时需要注意,由于LUT没有复位/置位端,因此描述RAM结构时不需要复位/置位信号。

Xilinx公司的这种分布式RAM结构在需要少量RAM的情况下可以代替Block RAM使用,毕竟在7系列FPGA中一块Block RAM就有36Kbits。以下列举了一些适用于分布式RAM的情况:

1. 深度小于64-bit

2. 在深度大于64-bit小于128-bit情况下,有时延要求并需要异步输出(其clock-to-out时间小,并且布线比Block RAM自由)

3. 数据宽度小于16-bit

/5

/5

文章评论(0条评论)

登录后参与讨论