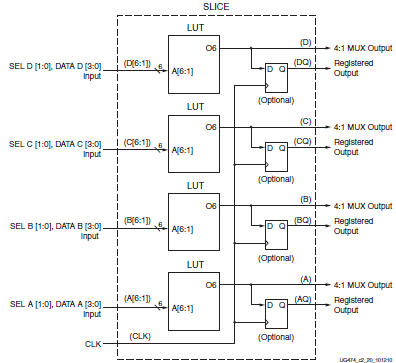

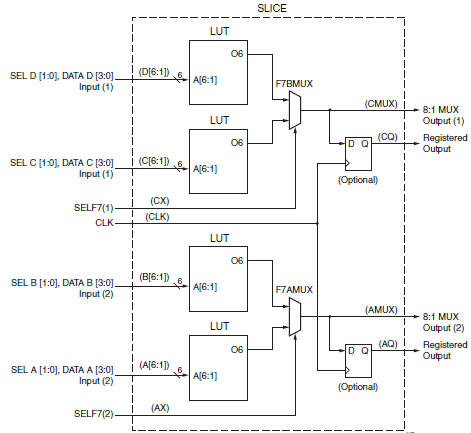

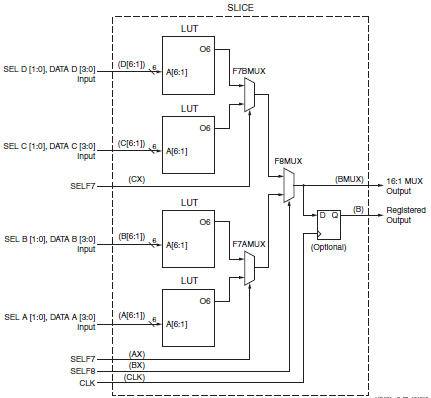

最近有幸与Xilinx的FAE交流了一次,收益颇多,其中讲到了Xilinx FPGA的内部结构,进一步加深了我对FPGA的认识。在Xilinx 7系列FPGA使用之CLB探索和(续)Xilinx 7系列FPGA使用之CLB探索中学习了CLB结构,竟然忽略了一个重要结构:多路复用器(multiplexer),在一个Slice中包含有三个多路复用器:F7MUXA、F7MUXB和F8MUX。其中F7MUXA组合LUT A和LUT B成为7输入LUT,F7MUXB组合LUT C和LUT D成为7输入LUT,而F8MUX组合1个Slice中的4个LUT成为8输入LUT。因此通过F7MUXA、F7MUXB和F8MUX的搭配,1个Slice可以实现4:1、8:1和16:1多路复用器,如图1、2、3所示。

图1 4:1 Multiplexer

图2 8:1 Multiplexer

图3 16:1 Multiplexer

在FPGA设计中需要多路选择时,可充分考虑此结构,比如地址译码电路,1个Slice最大能充当16:1的MUX,当超过16路选择时该如何处理呢?下面以实例来分析一下:

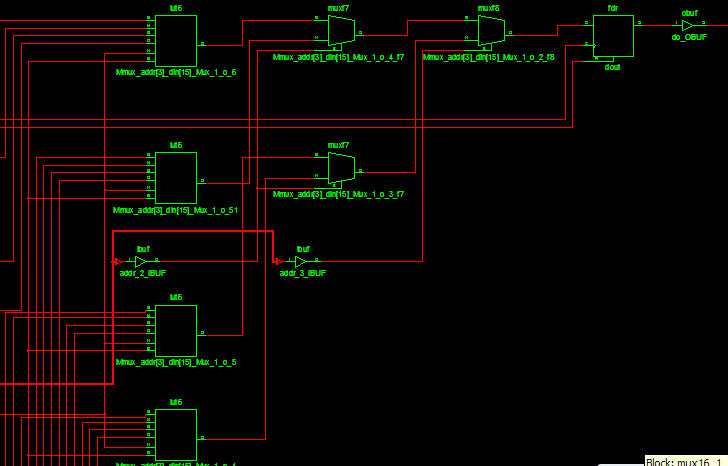

首先来看一下16:1的地址译码,程序如下,如图4所示为综合结果

module mux16_1(

input clk,

input rst,

input [3:0] addr,

input [15:0] din,

output do

);

reg dout;

always@(posedge clk)

if(rst)

dout<=1'b0;

else

case(addr)

4'b0000: dout<=din[0];

4'b0001: dout<=din[1];

4'b0010: dout<=din[2];

4'b0011: dout<=din[3];

4'b0100: dout<=din[4];

4'b0101: dout<=din[5];

4'b0110: dout<=din[6];

4'b0111: dout<=din[7];

4'b1000: dout<=din[8];

4'b1001: dout<=din[9];

4'b1010: dout<=din[10];

4'b1011: dout<=din[11];

4'b1100: dout<=din[12];

4'b1101: dout<=din[13];

4'b1110: dout<=din[14];

4'b1111: dout<=din[15];

endcase

assign do=dout;

endmodule

图4

与期望的相同,16:1 多路复用器可以通过4个LUT、2个F7MUX和1个F8MUX组合得到。

如果需要实现大于16:1的多路复用器该如何实现呢?试一下32:1,看综合器得到什么结果,程序如下,综合结果如图5所示。

module mux32_1(

input clk,

input rst,

input [4:0] addr,

input [31:0] din,

output do

);

reg dout;

always@(posedge clk)

if(rst)

dout<=1'b0;

else

case(addr)

5'b00000: dout<=din[0];

5'b00001: dout<=din[1];

5'b00010: dout<=din[2];

5'b00011: dout<=din[3];

5'b00100: dout<=din[4];

5'b00101: dout<=din[5];

5'b00110: dout<=din[6];

5'b00111: dout<=din[7];

5'b01000: dout<=din[8];

5'b01001: dout<=din[9];

5'b01010: dout<=din[10];

5'b01011: dout<=din[11];

5'b01100: dout<=din[12];

5'b01101: dout<=din[13];

5'b01110: dout<=din[14];

5'b01111: dout<=din[15];

5'b10000: dout<=din[16];

5'b10001: dout<=din[17];

5'b10010: dout<=din[18];

5'b10011: dout<=din[19];

5'b10100: dout<=din[20];

5'b10101: dout<=din[21];

5'b10110: dout<=din[22];

5'b10111: dout<=din[23];

5'b11000: dout<=din[24];

5'b11001: dout<=din[25];

5'b11010: dout<=din[26];

5'b11011: dout<=din[27];

5'b11100: dout<=din[28];

5'b11101: dout<=din[29];

5'b11110: dout<=din[30];

5'b11111: dout<=din[31];

endcase

assign do=dout;

endmodule

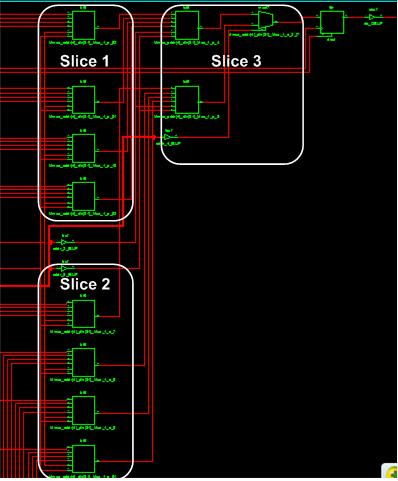

图5

实现32:1多路复用器使用了3个Slice,是4:1(Slice 1、Slice 2)和8:1(Slice 3)多路复用器的级联,综合器自动分析多路复用器达到了最优化的组合。

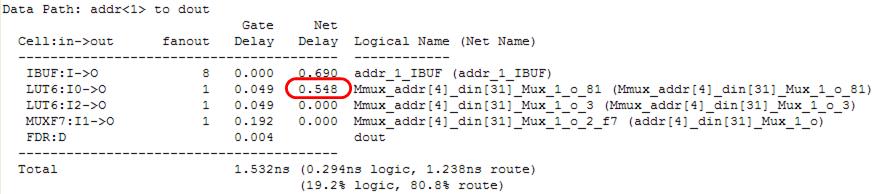

图6

如图6所示为32:1多路复用器数据路径的延时报告,其中LUT6和F7MUX的延时分别为0.049ns、0.192ns,LUT6与F7MUX之间的走线延时为0ns,相比于红框中的0.548ns忽略不计了,因为红框中的Net Delay是Slice外部的走线延时,LUT6与F7MUX之间的走线在Slice内部。因此,利用F7MUX、F8MUX实现的多路复用器缩短了逻辑延时,有利于时序收敛。

/5

/5

文章评论(0条评论)

登录后参与讨论