HDLC协议概述及其FPGA实现

引言

HDLC协议由于其简单可靠、有利于远程传输,在上个世纪末的窄带互联网时代被通信行业大规模采用。期间HDLC协议芯片也应运而生,由于其大大简化了HDLC通信系统的开发,从而进一步推动HDLC协议在通信中的运用。

当今宽带通信技术的快速发展,以太网迅速成为网络通信的主要手段,而HDLC协议失去电信领域这个最大市场,其芯片需求量急剧萎缩,厂商也停止对HDLC芯片的研发和生产。但是,在有些高可靠通信行业,如航空、航天、铁路等领域,HDLC协议依然是无法取代。在传输雷达信号数据、列车控制信号等关键场合,依然会采用HDLC通信系统。而曾经普遍使用的HDLC芯片均已停产多年,行业用户的HDLC通信系统保障,面临着巨大的隐患和风险。

FPGA即现场可编程门阵列,由于其可编程的特点,能够快速完成原型的开发。因此,使用FPGA实现HDLC协议成为一种可行的方案。

1 HDLC协议概述

高级数据链路控制(High-Level Data Link Control),是一个在同步网上传输数据、面向比特的数据链路层的协议,它是由国际标准化组织(ISO)根据IBM公司的SDLC(Synchronous Data Link Control)协议扩展开发而成的[1]。

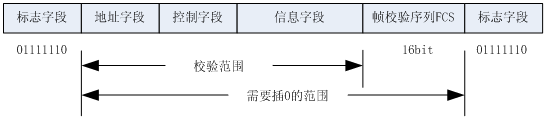

图 1 HDLC数据格式示意图

HDLC协议中数据按照帧为单位进行划分,如图1所示。

①、标志字段

标志字段用来表明一帧数据的边界,它由“0111_1110”组成,共8bit。该字段不允许出现在帧内部,以免引起歧义。为了保证它的唯一性,HDLC协议规定发送端中出现5个连“1”,则立即插入一个“0”;而接收端在发现5个连“1”后,即将后续的“0”删除。

②、内容字段

内容字段包括地址字段、控制字段和信息字段。地址字段表明数据发送的目的地址,共8bit;控制字段用于信令、应答和管理;信息字段即需要传递的数据。该字段的数据格式即可按照HDLC协议规范进行设计,如接收端和发送端都使用FPGA实现,也可定制一套数据格式用于传递。内容字段与协议的FPGA实现关联度较小,在此不再赘述。

③、帧校验序列FCS

帧校验序列用于监督本帧中的误码(标志字段不在监督范围内)。FCS规定采用循环冗余校验(Cyclic Redundancy Check,CRC)法,所用的循环码生成多项式规定为![]() 。

。

2 循环冗余编工作原理及电路设计

循环冗余编码(简称CRC)是一种常见的冗余编码,其基本工作原理是:将数据流的二进制除以生产多项式,商数被放弃,余数作为冗余编码追加到数据流后并进行发送。在接收端,新的数据流被同一生产多项式去除,检查余数是否为零。如果余数为零,则认为传输正确,否则就认为传输中出现差错,数据流重发[2]。

![]()

图 2 CRC编码生产电路结构图

CRC编码可以通过线性移位寄存器和异或门求得,线性移位寄存器移一位,完成一次除法,异或门则完成不带进位的减法。如果商数为1,则从被除数的高阶位减去除数,同时移位寄存器右移一位,准备为被除数的较低位进行运算。如果商数为0,则移位寄存器直接右移一位[3][4]。电路设计如图2所示。

3 HDLC的FPGA实现

3.1 HDLC发送端的FPGA实现

HDLC发送端接收总线上的并行数据(内容字段),经过功能模块处理按照HDLC帧格式串行输出。其结构示意图如图3所示,由四个功能模块和帧数据发送控制器组成。并行数据通过并串转换模块输出,在CRC16校验模块中产生16bit的校验位附着于后,经过插零、添加标志字段,最终完成HDLC帧格式数据输出。

图 3 HDLC协议发送端结构示意图

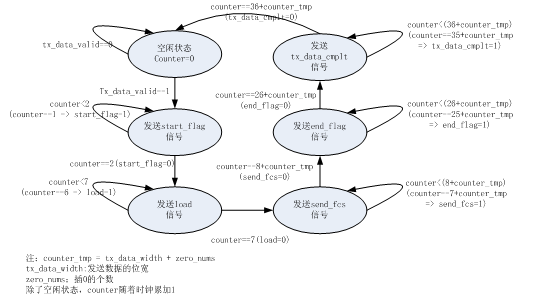

发送端**能模块间数据流的产生和协调由HDLC帧数据发送控制器进行控制的。当tx_data_valid信号有效(总线数据准备好)时,发送控制器开始按照图4所示的状态机进行切换,另外在脱离空闲状态时,启动一个计数器counter,用于向功能模块发送精准的控制信号。

图 4 HDLC发送端控制器状态机示意图

对图4中的控制信号进行说明:

load信号有效时,将并行数据加载寄存器中,然后数据由高位向低串行输出。

send_fcs信号用于输出信号的切换,当其无效时,CRC16模块输出上级输入数据;有效时,则输出CRC16校验字段。主要保证校验字段会附着在数据后串行输出。

当插零模块检测到连续5个1后,会进行插零操作,此时会发送block信号给并串转换模块和CRC16校验模块使其阻塞,完成插零操作后继续正常输出。

start_flag或者end_flag信号有效时,标志字段发生器都会输出01111110。

3.2 HDLC接收端的FPGA实现

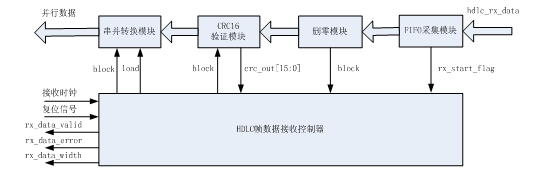

HDLC接收端从外部管脚获得帧数据,按照帧格式进行解析,得到内容字段发送至FPGA内部总线上。其结构示意图如图5所示,是由4个功能模块和帧数据接收控制器组成。接收端通过识别外部数据的标志位字段,将帧数据采集到FIFO中,完成一帧数据采集后在删零模块对多余的零进行删除,并对其数据进行CRC验证,后将数据放置的数据总线上。

图 5 HDLC协议接收端结构示意图

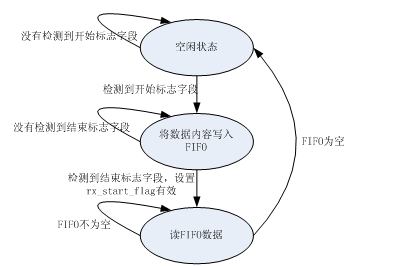

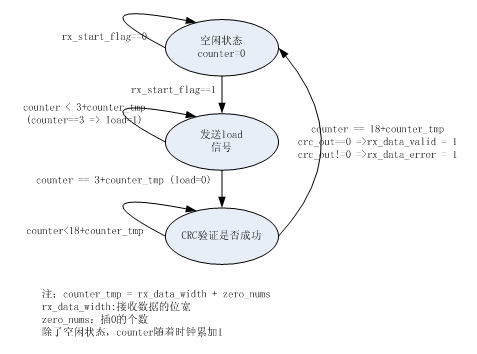

在接收端,由FIFO采集模块负责识别标志字段来判断数据帧的开始或者结束,在结束时发送rx_start_flag信号触发帧接收控制器,并从FIFO中读取数据发送给下一级模块。具体状态机切换如图6所示。

图 6 FIFO采集模块状态机示意图

接收端**能模块间数据流的产生和协调由HDLC帧数据接收控制器进行控制。当rx_start_flag信号有效时,接收控制器开始按照图7所示进行状态机切换,另外在脱离空闲状态时,启动一个计数器counter,用于向功能模块发送精准的控制信号。

图 7 HDLC接收端控制器状态机示意图

对状态机的控制信号进行说明:

rx_start_flag信号,是由FIFO采集模块向下一级模块发送数据时产生的,用于启动接收控制器。

load信号为数据进行串并转换的有效信号。

rx_data_valid信号有效说明信号CRC验证成功,接收数据有效。

rx_data_error信号有效说明信号CRC验证失败,接收数据存在错误。

4 结论

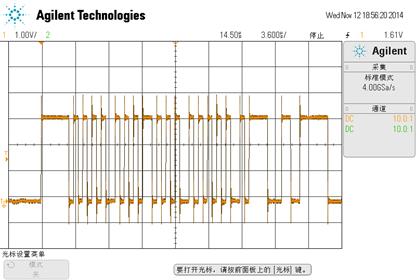

为了验证以上设计的正确性,本文采用Xilinx公司的Spartan6 XC6SLX4来实现HDLC协议,发送内容字段32bit 0xAA55AA55,采用CRC-16 CCITT-FALSE产生16bit的校验参数为0x4B6C,并依照协议添加标志位字段,发送的一帧数据应为0x7EAA55AA554B6C7E,发送速率为2Mhz。将程序下载执行,并将示波器探针放置在输出管脚上,得到输出波形如图8所示。验证了HDLC协议发送端结构设计是正确的。

图 8 FPGA发送帧数据波形图

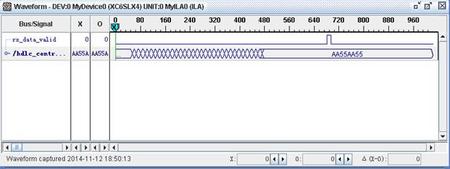

为了验证接收端结构设计的正确性,在硬件上将HDLC发送管脚和接收管脚相连,利用Xilinx公司的ChipScope软件去观察接收端的波形[5],采用rx_data_valid信号进行触发,通过图9可以观察到接收端已经将内容字段识别出来,和发送端的数据完全一致,这就验证了接收端设计的正确性。

图 9 FPGA接收端ChipScope观测波形图

另外,本文进一步的进行了回环测试,每40us发送一次,每次内容字段加一,经过5h时间的测试后,对比发送端和接收端的数据,没有发现丢数据包和错数据包的情况,根据以上测试结果可知,FPGA来实现HDLC协议是完全可行的方案。

/5

/5

文章评论(0条评论)

登录后参与讨论