<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" /><?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

附件是PDF文档。

上次对EP<?xml:namespace prefix = st1 ns = "urn:schemas-microsoft-com:office:smarttags" />1C3T144C8中的CLK和PLL的所有管脚做了分析,有几个管脚分析错了,谢谢 coyoo 朋友指出。今天就在把芯片中的电源管脚拿出来分析下。

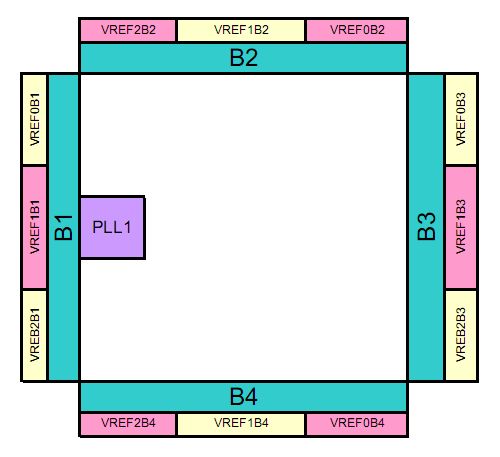

直接上图:

用红色箭头标明的是 VCCIO[1..4]

用黑色箭头标明的是 GND

用蓝色箭头标明的是 VCCINT

用绿色箭头标明的是 VREF[0..2]B[1..4]

下面的内容也是来自Altera文档

Pin Information For The Cyclone? EP1C3 Device

Bank Number VREF Bank Pin Name/Function Optional Function(s) T144

B1 VREF0B1 VCCIO1 pin 8

B1 VREF2B1 VCCIO1 pin 29

B2 VREF0B2 VCCIO2 pin 115

B2 VREF2B2 VCCIO2 pin 137

B3 VREF2B3 VCCIO3 pin 81

B3 VREF0B3 VCCIO3 pin 102

B4 VREF2B4 VCCIO4 pin 44

B4 VREF0B4 VCCIO4 pin 66

VREF2B4 VCCINT pin 46

VREF0B4 VCCINT pin 64

VREF0B2 VCCINT pin 117

VREF2B2 VCCINT pin 135

B1 VREF0B1 GND pin 9

B1 VREF2B1 GND pin 30

B2 VREF0B2 GND pin 116

B2 VREF2B2 GND pin 138

B3 VREF2B3 GND pin 80

B3 VREF0B3 GND pin 101

B4 VREF2B4 GND pin 43

B4 VREF0B4 GND pin 65

VREF2B4 GND pin 45

VREF0B4 GND pin 63

VREF0B2 GND pin 118

VREF2B2 GND pin 136

B1 VREF0B1 IO VREF0B1 pin 5

B2 VREF0B2 IO VREF0B2 pin 120

B3 VREF0B3 IO VREF0B3 pin 104

B4 VREF0B4 IO VREF0B4 pin 61

B2 VREF1B2 IO VREF1B2 pin 125

B3 VREF1B3 IO VREF1B3 pin 96

B4 VREF1B4 IO VREF1B4 pin 56

B2 VREF2B2 IO VREF2B2 pin 133

B3 VREF2B3 IO VREF2B3 pin 79

B4 VREF2B4 IO VREF2B4 pin 48

Pin Information for the Cyclone? EP1C3T144 Device

下面是管脚的信息:

Pin Name Pin Type (1st, 2nd, &3rd Function)

VCCIO[1..4] Power

Pin Description

These are I/O supply voltage pins for banks 1 through 4. Each bank can support a different voltage level. VCCIO supplies power to the output buffers for all I/O standards. VCCIO also supplies power to the input buffers used for the LVTTL, LVCMOS, 1.5-V, 1.8-V, 2.5-V, and 3.3-V PCI I/O standards.

这些I/O给给个bank提供参考电压。每个bank可以支持的电压标准,但是每个bank内部的电压都是一样的。VCCIO为输出缓冲区的所有I/O提供电压标准。VCCIO还可以为输入缓冲区I/O提供各种不同的电压标准,如LVTTL, LVCMOS, 1.5-V, 1.8-V, 2.5-V, and 3.3-V PCI各种I/O标准。

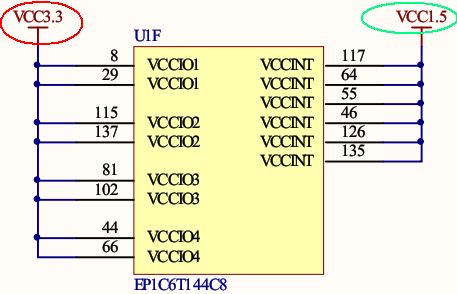

不过我们用的开发板一般基本上每个bank用的都是一样的电压标准,如

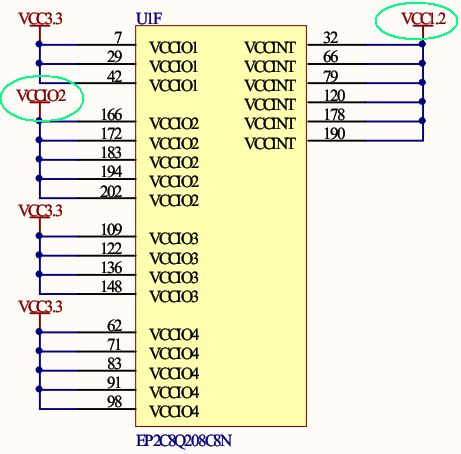

也有不一样的,

也有不一样的,

在来补充:

The Cyclone II VCCINT pins must always be connected to a 1.2-V power supply. If the VCCINT level is 1.2 V, then input pins are 1.5-V, 1.8-V, 2.5-V, and 3.3-V tolerant. The VCCIO pins can be connected to either a 1.5-V, 1.8-V, 2.5-V, or 3.3-V power supply, depending on the output requirements. The output levels are compatible with systems of the same voltage as the power supply (i.e., when VCCIO pins are connected to a 1.5-V power supply, the output levels are compatible with 1.5-V systems). When VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3-V and is compatible with 3.3-V systems.

Cyclone II器件的 VCCINT管脚必须一直连接到1.2V电源上。如果VCCIO连接的是1.2V电源,那么输入管脚可以兼容1.5-V, 1.8-V, 2.5-V, 和3.3-V。VCCIO管脚既可以连接到1.5-V, 1.8-V, 2.5-V, 或者 3.3-V提供电压,还可以根据输出的需求来调整VCCIO的输入电压。输出电压和VCCIO提供的电压是兼容的(当VCCIO管脚连接到1.5V的电源上时,输出电压也是1.5V,与系统提供的电源电压兼容)。当VCCIO管脚连接到3.3V的电源上时,输出的高电平也是3.3V,也与系统提供的电源电压兼容。

Pin Name Pin Type (1st, 2nd, &3rd Function)

VCCINT Power

Pin Description

These are internal logic array voltage supply pins. VCCINT also supplies power to the input buffers used for the LVDS, SSTL2, and SSTL3 I/O standards.

The Cyclone II VCCINT pins must always be connected to a 1.2-V power supply.

Cyclone II器件的 VCCINT管脚必须一直连接到1.2V电源上。

这些管脚是给内部逻辑阵列提供电压,就是FPGA芯片内核电压。不同芯片的内核电压不一样,上图中的EP1C就是1.5V,EP2C就是1.2V。VCINT还为用LVDS,SSTL2和SSTL3 当做I/O标准的输入缓冲区提供电压。

Pin Name Pin Type (1st, 2nd, &3rd Function)

GND Ground

Pin Description

Device ground pins. All GND pins should be connected to the board GND plane.

芯片接地引脚。所有的GND管脚都应该接到板子的地平面。

Pin Name Pin Type (1st, 2nd, &3rd Function)

VREF[0..2]B[1..4] I/O, Input

Pin Description

Input reference voltage for banks 1-4. If a bank uses a voltage-referenced I/O standard, then these pins are used as the voltage-reference pins for the bank. If voltage reference I/O standards are not used in the bank, the VREF pins are available as user I/O pins.

给每个bank输入参考电压。如果一个bank使用参考电压的I/O标准,那么这些管脚就是用来输入参考电压。如果bank用的不是参考电压的I/O标准,则VREF管脚可以当做普通的I/O口。

下面这段话也是来自Altera的手册中:

To accommodate voltage-referenced I/O standards, each Cyclone II I/O bank has a VREF bus.

为了调节参考电压的I/O标准,Cyclone II器件的每个bank有VREF的总线。

疑惑:一般这些管脚都被我们用来当普通的I/O口,但是我还是不太明白 用作输入参考电压的意思,

前面的VCCIO管脚就是为每个bnak提供输入和输出电压标准的,这样的话,VREF管脚究竟是用来干什么的?这个我还是不太清楚。希望知道的朋友能指点。

/2

/2

用户377235 2014-5-19 09:02