对传输线进行特性阻抗(Z)控制是RF及高速数字电路设计中的重要一环。良好的阻抗匹配能够显著减少高频高速信号的反射,从而避免出现信号完整性问题。在pcb设计的过程中,我们经常会遇到共面阻抗的情况。

例如双层板做单端50欧的阻抗控制,我们知道,对传输线特性阻抗影响最大的因素是耦合平面的高度(H),为了保证PCB的机械强度,PCB不可能做得很薄,这就造成了双面板的耦合平面高度(H)偏大,对导线的耦合影响大大降低,所以这时候板厚(H)对阻抗的影响非常小,从而造成了在单端50欧阻抗时,线宽明显偏大,导致PCB设计不合理。这时,我们就应该采用共面阻抗的特性,通过单端导线周边的包裹铜箔对导线产生耦合电容,从而降低pcb导线的阻抗,换句话说,即在满足单端50阻抗控制时,降低pcb导线的宽度。

微带线单端特性阻抗-Polar 9000

共面波导特性阻抗–Polar 9000

另一种常见的情形是,采用非共面阻抗进行阻抗控制时,就要避免同层的铜箔过于接近传输线,从而对阻抗造成不良的影响,例如4层板的DDR传输线做阻抗控制,在覆铜时就要在传输线区域画禁止覆铜区以避免铜箔对导线造成阻抗失调的影响, 导线边缘离铜箔边缘至少1倍线宽的距离。

DDR 区域添加禁止铺铜区

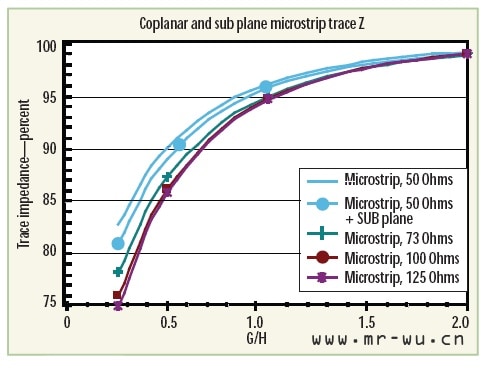

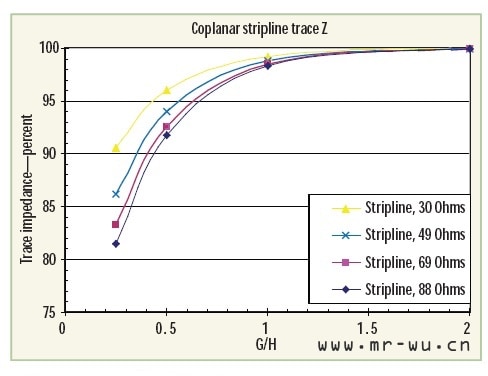

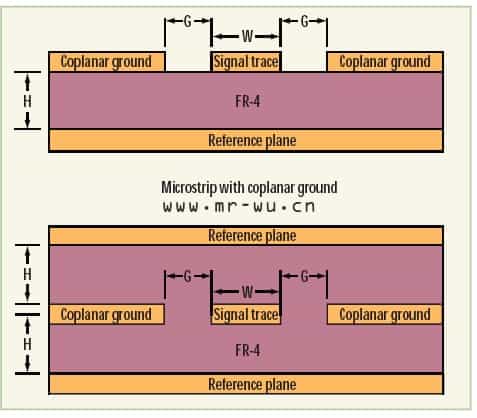

记住,紧挨的铜箔会对传输线的特性阻抗造成影响,距离越近,耦合电容越强,从而特性阻抗越低。我们有时候需要利用这个特性,而有时候又要避免这个特性对阻抗造成负面影响。我们还可以结合铜箔与传输线间距(G)与 参考平面与传输线的高度(H)这两个因素,对传输线进行阻抗控制。

微带线与铜箔间距和铜箔高度之间的阻抗变化曲线

带状线与铜箔间距和铜箔高度之间的阻抗变化曲线

传输线与铜箔间距

原创文章,转载请注明: 转载自 吴川斌的博客 http://www.mr-wu.cn/

本文链接地址: 论共面阻抗对高频高速PCB设计中传输线的阻抗控制影响 http://www.mr-wu.cn/gauge-effects-coplanar-ground-planes/

/5

/5

文章评论(0条评论)

登录后参与讨论