背板是一种典型的用于系统内汇集所有电子模块的物理互连的方式。复杂的系统依靠背板上的连线、走线和连接器 来处理大量的高速数据。多个背板模块之间的通信受到诸如连接器、走线长度、过孔和终端等部件的阻抗、电容以 及电感参数的影响。设计高性能分布式负载背板的一个极为重要的因素是要了解如何进行设计来保证良好的信号完 整性。

本技术说明介绍了几种拓扑连接结构间的基本区别。说明了在背板设计时需要考虑到的各种问题,并重点讨论了通 过背板以点对点的传输线方式进行连接时的关键问题。包括印刷电路板走线结构、过孔、器件封装和背板连接器等 方面。我们还为设计师们提供了一份印刷电路板设计的检查清单。给出了针对某些特定频率的讨论和指导。本文档 还讨论了莱迪思半导体公司的 FPGA 产品线及其 SERDES 高速背板接口。这些接口通过 CML 差分缓冲接口提供高 速串行数据流。

文章目录 [显示]

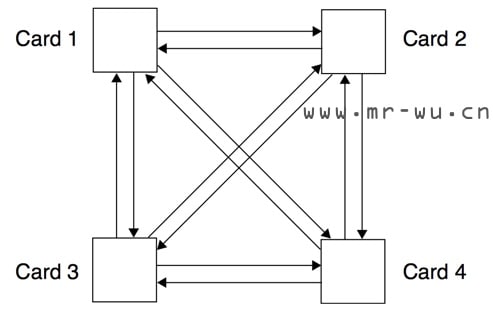

目前背板的系统互连拓扑结构主要有三种。它们分别是多点对多点、一点对多点和点对点。传统系统使用多点对多点 / 一点对多点连接的拓扑结构,为带有单个网络 (节点)的多个器件提供有效的互连和通信,如图 1 所示。

多点对多点背板结构

然而,这种网络结构有严格的数据速率限制。每个网络在卡与背板连接的节点上会有 T 型结构或者分支结构。这些 T 型结构会导致背板上信号路径传输线的不连续和不匹配。结果就会在高速传输时,卡与背板接口上都有大反射信 号。这些反射信号会来回传送,持续较长的时间,在高速传输的情况下严重降低了信号的完整性。通常要等所传输 数据的每个位的反射信号逐渐衰减后,才能实现可接受的信号通信。这大大限制了通信速率。因此,多点对多点和 一点对多点的拓扑结构的速率极限一般都低于 100 Mbps。由于实际走线长度和卡的插槽的增加,该速度极限很容易 就会低于 10 Mbps。

点对点的互连拓扑结构消除了上面所述的信号路径的分支。消除了所产生的信号反射,从而大大提高了最大的数据 速率。通过周详的设计考虑,这种背板互连可用于数据速率高达 3 Gbps 甚至更高的通信。

这种方法的缺点是增加了背板走线和卡上端口的接口数。一个多点连接的背板上 n 个插卡互连的网络,必须使用 n (n-1)个单向点对点的连接来代替。每个插卡必须提供 n-1 个发送和 n-1 个接收端口,用于整个系统的互连。例如:一个四块印刷电路板的系统的全互连如图 2 所示。

四个插卡的点对点互连系统

每个插卡必须提供 3 个发送器和 3 个接收器端口。每条带箭头的线代表一个点对点的背板网络。

如今的通信设备设计已经呈现对于印刷电路板之间更高带宽互连的需求。快速发展的 IC 技术,随着其拥有数千兆位 的处理和驱动能力,点对点的背板拓扑结构成为了许多当今新型硬件系统的理想选择。这种拓扑结构对于串行和并 行的数据结构都提供支持。莱迪思半导体公司日前推出多款具有多个端口的 IC 产品,每个端口可实现高达 Gbps 的 背板驱动能力。这些器件将在后文中进行介绍。本文的稍后部分将侧重讨论点对点背板互连的印刷电路板设计。

典型的点对点拓扑结构采用了简单、单路径互连结构,从一块卡的发送器件通过背板,传输到另一块卡的接收器件。

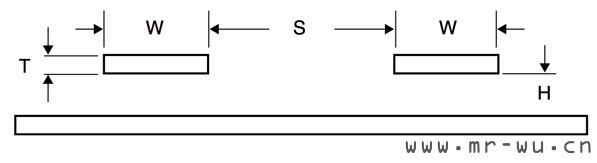

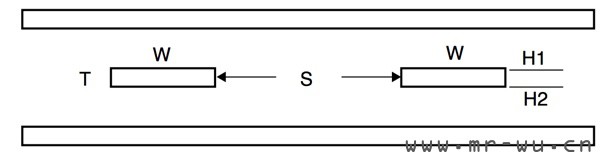

这样一个互连的实际物理路径如图 3 所示。

互连的实际物理结构

点对点互连单元都是串行连接的,并提供一个单一的信号路径。每个单元可以被认为是一个传输线区段。理想情况 下,通过控制和匹配每个传输线区段的特性阻抗,可创建一条一致的电子信号路径。然后信号可以沿路径传播,而 不会发生信号反射。在接收器件输入端添加一个终端电阻,其大小等于传输线的特性阻抗,这样可以实现发送器和 接收器之间最大带宽的无失真数据连接通道。

图 3 中的每个单元都可以被分解成若干个子单元。例如:对信号路径影响最大的印刷电路板传输线部分,包括的子 单元有:金属走线、绝缘层、接地层和 (层间)过孔。每个子单元都是信号路径的重要组成部分,并且如果没有妥 善的设计,可能导致电子信号路径的不连续性和信号反射。图 3 中的单元和子单元的设计问题,将在下文中的几个 章节进行讨论。

关于使用差分信号互连方案的系统的优势,在电子设计的各个领域都是众所周知的。这些优势对于高带宽、高密度, 同时需要极低错误率的数据链路的硬件系统来说是非常重要的。差分信号可以不受共模噪声的影响,而共模噪声在 大多数应用系统中广泛存在。例如,使用差分信号避免了传统的 “ 地反弹 ” 的噪声问题,这正是许多使用单端接口的 高密度 IC 所面临的问题。差分信号也提供了更高的噪声容限,从而使数字链路的位错误率更低。随着由于需要支持 更高的带宽,信号的边沿速率随之提高,印刷电路板设计还需要为板上的电感耦合电流提供返回回路。因为电流仍 然是局部性的,差分信号有助于减少这个感应电流引起的 “ 反弹 ”。这是因为差分对的一端是吸入电流而另一端是源 电流,从而从根本上消除了感应电流的影响。差分信号互连方法应被用于所有关键的高速互连。

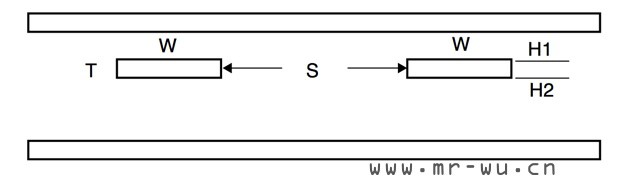

阻抗受控的差分信号走线对有许多种不同的配置方式。下面是最常见的四种方式。

边缘耦合的微带方式 (表面走线)

边缘耦合的带状线方式 (夹在两个参考平面之间)

偏

原创文章,转载请注明: 转载自 吴川斌的博客 http://www.mr-wu.cn/

本文链接地址: 高速印刷电路板的设计考虑–分享至莱迪思半导体的应用笔记 http://www.mr-wu.cn/highspeed-pcb-design-considerations/

/2

/2

文章评论(0条评论)

登录后参与讨论