写在前面的话:在学习电子的时候走了很多弯路,现在想想非常感谢关心过我的人,我真的很感谢他们,但是现在回想起来确实可以让路走的更直一点。

图 1-1

图 1-1

首先现在知道的是S3C2440拥有2个锁相环,一个是MPLL,一个是UPLL。

MPLL用于 CPU及其他外围器件。UPLL用于USB提供48MHz.外部时钟源经过MPLL处理后能够得到三种不同的系统时钟。他们分别是FCLK,HCLK,PCLK三种频率,这三种频率分别有不同的用途。

FCLK是CPU提供时钟信号。主频时钟用于ARM920T内核。

HCLK是为AHB总线提供的时钟信号,主要用于高速外设,比如内存控制器,中断控制器,LCD控制器,DMA以及USB主模块等。

PCLK是为APB总线提供的时钟信号,主要用于低速外设,比如看门狗,UART控制器,IIS,I2C,SDI/MMC,GPIO,RTC and SPI。

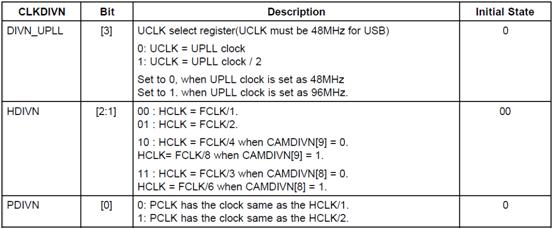

这三个系统时钟具有一地定的比例关系,这种关系是通过寄存器CLKDIVN中的HDIVN位和PDIVN位来控制的,因此我们知道了FCLK,再通过这2为的控制就能确定HCLK,PCLK.而FCLK则是通过外部时钟源的频率,经过一个计算公式来得到的。

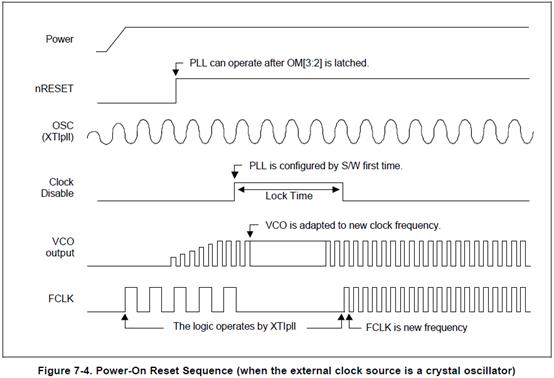

S3C2440的时钟源可以由晶振电路提供还可以选择用外部时钟来提供,图1-2所示即为2种时钟源的提供方式。

图 1-2

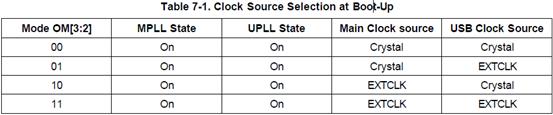

S3C2440的时钟可以选用晶振(XTAL),也可以使用外部时钟(EXTCLK),由系统复位时,在复位信号上升沿对引脚OM3、OM2所测的状态来确定。其对应关系如表2-1所示

|

OM[3:2]值 |

主时钟源 |

USB时钟源 |

|

00 |

<?xml:namespace prefix = st1 />Crystal |

Crystal |

|

01 |

Crystal |

EXTCLK |

|

10 |

EXTCLK |

Crystal |

|

11 |

EXTCLK |

EXTCLK |

表 1-1

图 1-3

上图1-3所示的即是时钟选择控制位的真值表。即是确定时钟来源的控制位。

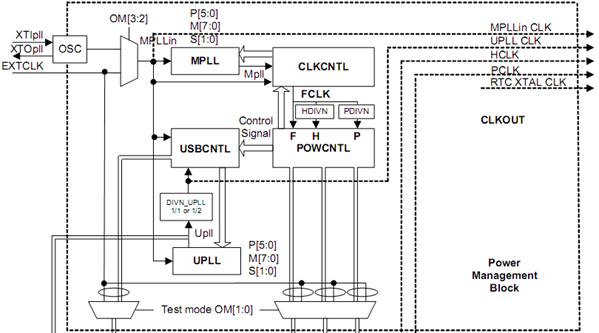

图 1-4 时钟发生器框图

图 1-4 时钟发生器框图

从图1-4中我们可以看出S3C2440含有两个锁相环MPLL、UPLL产生系统所需要的时钟。

MPLL:FCLK—CPU,HCLK—AHB总线,PCLK—APB总线

UPLL: USB 产生UCLK (48MHz)CAM摄像头。

(1) 使用HCLK的设备:

中断控制器、存储器管理器、DMA控制器、LCD控制器、FLASH控制器、USB Host(不用PLL时)、总线控制器、片外设备.

(2) 使用PCLK的设备:

117个通用I/O口GPIO、ADC、5个定时器与4个PWM、3个UART、2个SPI、IIC、USB Device (不用PLL时)、RTC、WDT、SD卡接口、IIS接口(Host and Device).

图 1-5 时钟频率管理

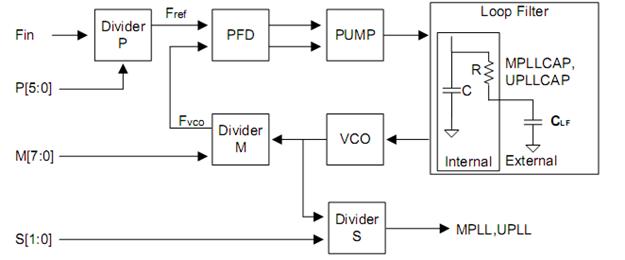

(1)锁相环输出频率

MPLL =(m×Fin×2)/(p×2S)

m = M+8, M:M寄存器的值

p = P+2, P:P寄存器的值

S:S寄存器的值

看了这么久得理论,最终还是得看懂代码的。

mpll_val = (92<<12)|(1<<4)|(1);

//////////////////////////////////////////////////////////

//101 1100 0000 0000 0000

// 1 0000

// 1

//101 1100 0000 0001 0001

//////////////////////////////////////////////////////////

//init FCLK=400M, so change MPLL first

确定时钟频率最关键的代码的就是下面的两句了

ChangeMPllValue((mpll_val>>12)&0xff, (mpll_val>>4)&0x3f, mpll_val&3);

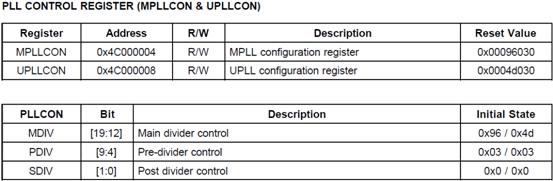

上面调函数实现了MDIV=92 PDIV=1 SDIV=1从而计算MPLL和UPLL的值。

m=(MDIV+8)=100, p=(PDIV+2)=3,s=SDIV=1.

ChangeClockDivider(key, 12);

我再找出函数的原型分析下,

//*************************[ MPLL ]*******************************

下面这个函数就是确定MPLLCON寄存器的值也就是确定MDIV、PDIV、SDIV的值。

void ChangeMPllValue(int mdiv,int pdiv,int sdiv)

{

rMPLLCON = (mdiv<<12) | (pdiv<<4) | sdiv;

}

///////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

下面这个函数就是改变FCLK和HCLK和PCLK之间的比例关系

void ChangeClockDivider(int hdivn_val,int pdivn_val)

{

int hdivn=2, pdivn=0;

// hdivn_val (FCLK:HCLK)ratio hdivn

// 11 1:1 (0)

// 12 1:2 (1)

// 13 1:3 (3)

// 14 1:4 (2)

// pdivn_val (HCLK:PCLK)ratio pdivn

// 11 1:1 (0)

// 12 1:2 (1)

switch(hdivn_val) {

case 11: hdivn=0; break;

case 12: hdivn=1; break;

case 13:

case 16: hdivn=3; break;

case 14:

case 18: hdivn=2; break;

}

switch(pdivn_val) {

case 11: pdivn=0; break;

case 12: pdivn=1; break;

}

rCLKDIVN = (hdivn<<1) | pdivn;

switch(hdivn_val) {

case 16: // when 1, HCLK=FCLK/6.

rCAMDIVN = (rCAMDIVN & ~(3<<8)) | (1<<8);

break;

case 18: // when 1, HCLK=FCLK/8.

rCAMDIVN = (rCAMDIVN & ~(3<<8)) | (1<<9);

break;

}

if(hdivn!=0)

MMU_SetAsyncBusMode();

else

MMU_SetFastBusMode();

}

上面已经计算出来m=(MDIV+8)=100, p=(PDIV+2)=3,s=SDIV=1.

m p s 的值,从而可以得出 MPLL=(2*100*12)/(3*1)=400MHZ

m=77+8=85,p=5,s=0

UPLL=(85*12)/(5*1)=97/5=

FCLK=400MHZ

又因为FCLK:HCLK:PCLK的分频比为1:4:8,从而得到HCLK的值为100MHZ,PCLK的值为50MHZ。

(2)S3C2440内核时钟频率

使用锁相环:FCLK=MPLL

慢模式下: FCLK=MPLL/除数器比率

图 1-6 锁相环(倍频器)工作原理图

(1) 正常模式 NORMAL

锁相环工作

为CPU和所有片内外设提供时钟

此模式系统功耗最大

NORMAL:这个模块支持CPU时钟以及2440相应的外围设备时钟。这个模式下,电源消耗是最大的。它允许通过软件编程来控制外部设备的操作。例如,如果一个定时器Timer不需要时,那么用户可以通过CLKCON寄存器来关闭时钟和Timer相连,来降低电源消耗。

(2) 慢时钟模式 SLOW

锁相环不工作

CPU等直接使用原始时钟、或原始时钟的分频工作,此模式工作时钟频率低而使功耗低,并且锁相环不工作也使功耗降低.

SLOW模式:又叫NON-PLL模式,不同于Normal模式,这个模式使用的时一个外部时钟来直接驱动2440的主频FCLK,不通过PLL,在这个模式下,电源的消耗仅仅和外部时钟频率有关,电源同PLL有关的消耗可以忽略。

(3) 空闲模式 IDLE

停止为CPU提供时钟,CPU不工作(其它外设均工作).

退出方法:

任何中断请求可唤醒CPU工作,退出空闲模式。

IDLE模式:这个模式下CPU的时钟FCLK被关闭,而其他外围设备的时钟还继续工作。因此空闲模式的结果只是能够降低CPU核的电源消耗。注意,任何中断请求都能够将CPU唤醒。

(4) 掉电模式 SLEEP

时钟模块断电,除了唤醒电路之外所有部分均不供电

系统需分成两部分供电。此模式功耗最低

退出方法:用中断唤醒必须设置外中断

(1)外部中断EINT0---15

(2)实时钟报警中断

Sleep模式:这个模式关闭了内部电源。因此CPU&内部的逻辑单元都没有电源消耗,除了工作在这个模式下的一个wake-up逻辑单元。因此sleep模式需要2个独立的电源。一个来支持wake-up模块工作,另外一个支持内部逻辑&CPU的电源,并且这个模块的电源是可控的。所以在Sleep模式,支持内部逻辑&CPU的电源模块是关闭的,而通过EINT[15:0]&RTC中断可以从Sleep模式唤醒。

例如我们的手机来说就是如果空闲5秒钟或是更长时间背光就没了,也是通过电源模式的变化实现的。系统的功耗从而得到很好的控制了。

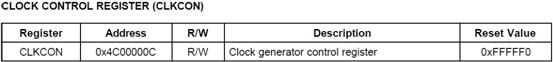

S3C2440的时钟与电源管理共有6个专用寄存器,其基地址均为0x4C000000。

|

寄存器 |

R/W |

描 述 |

初值 |

偏址 | |

|

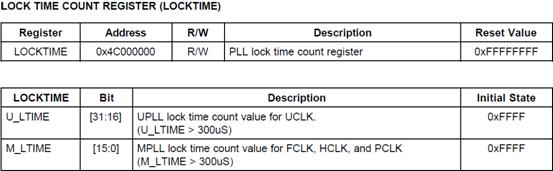

LOCKTIME |

R/W |

PLL锁定时间寄存器 |

0x00FFFFFF |

0x00 | |

|

MPLLCON |

R/W |

MPLL配置寄存器 |

0x0005C080 |

0x04 | |

|

UPLLCON |

R/W |

UPLL配置寄存器 |

0x00028080 |

0x08 | |

|

CLKCON |

R/W |

时钟控制寄存器 |

0x0007FFF0 |

0x0C | |

|

CLKSLOW |

R/W |

慢时钟控制寄存器 |

0x00000004 |

0x10 | |

|

CLKDIVN |

R/W |

时钟比控制寄存器 |

0x00000000 |

0x14 | |

表 1-2 6个寄存器

图 1-7

LOCKTIME:锁定时间,即锁相环从启动到正常工作所需的时间,一般保持默认,即0xFFF即可。

图 1-8

图 1-9

锁相环输出频率设置:

MPLL =(m×Fin×2)/(p×2S)

m=MDIV + 8, p=PDIV + 2; s=SDIV

UPLL = (m×Fin)/(p×2S)

m=MDIV + 8, p=PDIV + 2; s=SDIV

用于控制各模块是否有频率输入,一般保持默认即可

图 1-10 时钟控制寄存器

图 1-11 时钟控制寄存器

Bit3: 1:进入睡眠模式

Bit2:1 进入特别模式(保留模式,没有使用)

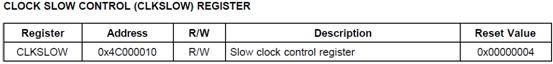

慢时钟模式,用于设置与慢时钟模式相关的配置信息。

图 1-12慢时钟控制寄存器CLKSLOW

图 1-13

进入慢速模式后,需要手动关闭锁相环。还需设置实际的时钟频率。

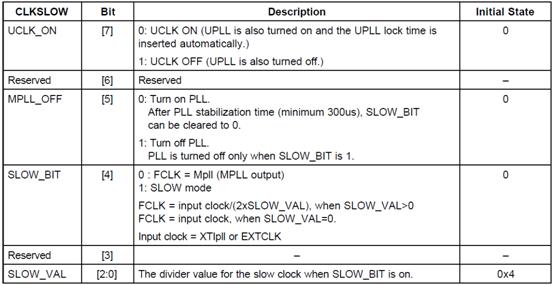

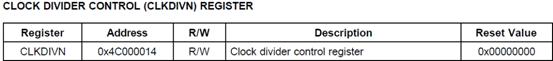

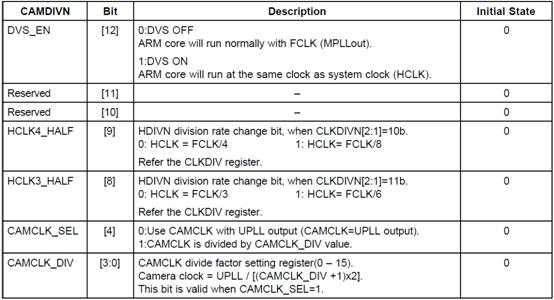

用于控制HCLK、PCLK、FCLK之间的分频比,共有以下几种

图1-14

图1-15

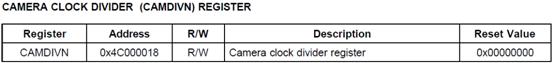

用于控制摄像头分频比

图1-15 CAM控制寄存器

图 1-17

/4

/4

文章评论(0条评论)

登录后参与讨论