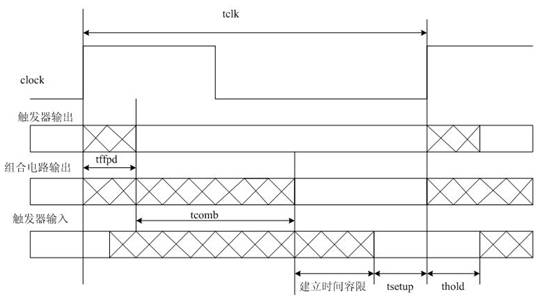

图 3-1

图3-1所示的即为

Tffpd:触发器输出的响应时间,也可以理解为触发器输出在clk上升沿到来后的时间内发生变化, 之后稳定,也可以理解输出延迟。

Tcomb: 触发器输出的变化经过组合逻辑元件所需的附加时间,也就是题目中的组合逻辑延迟

tsetup:建立时间

thold:保持时间

tclk: 时钟周期

建立时间容限:这里用容限的概念是为了数学推导方便,时间容限仅仅是一个概念,在这里我们对建立时间容限的要求是大于0,当然有的地方可能就是小于0了。

图 3-2

建立时间(setup time):是指在触发器的时钟信号上升沿到来之前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;

保持时间(hold time): 是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够数据同样不能被打入触发器。

有个网友说的很有意思,他是这样理解的就是建立时间就是跳楼的过程,不知道是几楼,等你挂在地上时就是0保持时间了。这个说法很是犀利啊。

/4

/4

文章评论(0条评论)

登录后参与讨论