本文内容

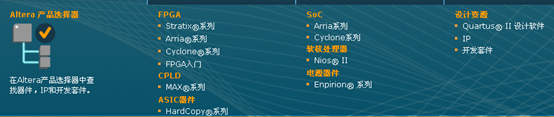

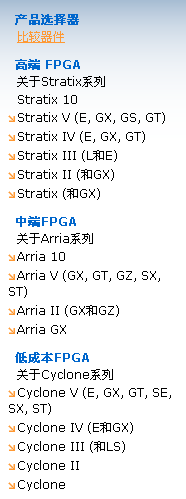

1,altera产品线和选型工具

2,cyclone ii特点

3,cyclone ii引脚

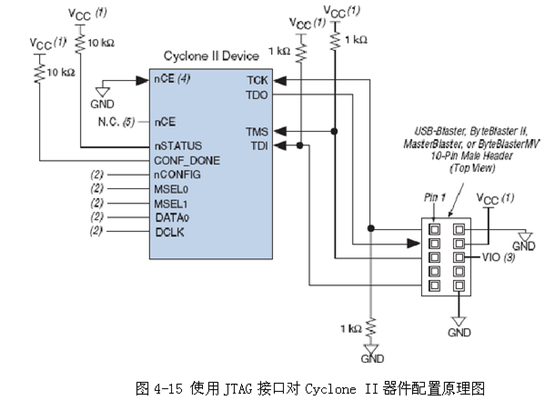

4,cyclone ii调试和配置电路

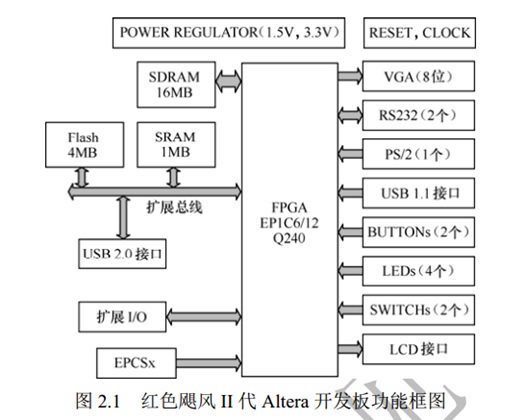

5,cyclone ii最小系统和实现方案

6,PCB SMT设计注意事项

官网选型工具和芯片分类

ALTERA FPGA产品线

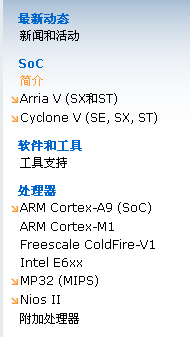

SOC

根据控制器划分

飓风II特点

在线查看 http://www.bdtic.com/ALTERA/CycloneII/index.html

可参考资料:

宣传手册2013 product-altera.pdf

Cyclone II Device Family Data Sheet (cyc2_cii5v1_01.pdf)

Cyclone II Device Handbook, Volume 1 (cyc2_cii5v1.pdf)

|

表1. Cyclone II FPGA简介 | ||||||

|

器件 |

EP2C5 |

EP2C8 |

EP2C20 |

EP2C35 |

EP2C50 |

EP2C70 |

|

逻辑单元 |

4,608 |

8,256 |

18,752 |

33,216 |

50,528 |

68,416 |

|

M4K RAM块 |

26 |

36 |

52 |

105 |

129 |

250 |

|

总比特数 |

119,808 |

165,888 |

239,616 |

483,840 |

594,432 |

1,152,000 |

|

嵌入式18x18乘法器 |

13 |

18 |

26 |

35 |

86 |

150 |

|

PLLs |

2 |

2 |

4 |

4 |

4 |

4 |

|

最多用户I/O 管脚 |

142 |

182 |

315 |

475 |

450 |

622 |

|

差分通道 |

58 |

77 |

132 |

205 |

193 |

262 |

|

提供日期 |

现在 |

现在 |

现在 |

现在 |

现在 |

现在 |

|

表2. Cyclone II器件封装和最多用户I/O管脚 | ||||||

|

封装尺寸 |

EP2C5 |

EP2C8 |

EP2C20 |

EP2C35 |

EP2C50 |

EP2C70 |

|

144-Pin TQFP |

89 |

85 |

|

|

|

|

|

208-Pin PQFP |

142 |

138 |

|

|

|

|

|

240-Pin PQFP |

|

|

142 |

|

|

|

|

256-Pin FineLine BGA |

158 |

182 |

152 |

|

|

|

|

484-Pin Ultra FineLine BGA |

|

|

|

322 |

294 |

|

|

484-Pin FineLine BGA |

|

|

315 |

322 |

294 |

|

|

672-Pin FineLine BGA |

|

|

|

475 |

450 |

422 |

|

896-Pin FineLine BGA |

|

|

|

|

|

622 |

|

表3. Cyclone II FPGA的适用配置器件 | ||||||

|

配置器件 |

支持Cyclone II器件 | |||||

|

EP2C5 |

EP2C8 |

EP2C20 |

EP2C35 |

EP2C50 |

EP2C70 | |

|

EPCS1 |

X |

|

|

|

|

|

|

EPCS4 |

X |

X |

X |

|

|

|

|

EPCS16 |

X |

X |

X |

X |

X |

X |

|

EPCS64 |

X |

X |

X |

X |

X |

X |

飓风 II管脚

Cyclone II EP2C5 Device Pin-Out PT-EP2C5-2.0 (见附件)

特殊引脚

http://wenku.baidu.com/view/20e18e8fa0116c175f0e4838.html

引脚兼容和特殊引脚

(1) Cyclone II devices support vertical migration within the same package (for example, you can migrate between the

EP2C20 device in the 484-pin FineLine BGA package and the EP2C35 and EP2C50 devices in the same package).

(2) The Quartus II software I/O pin counts include four additional pins, TDI, TDO, TMS, and TCK, which are not available as general purpose I/O pins.

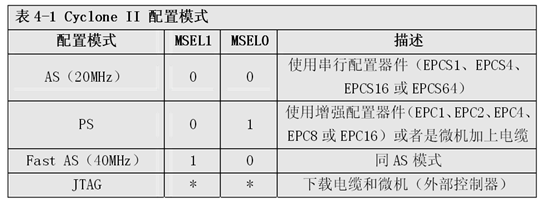

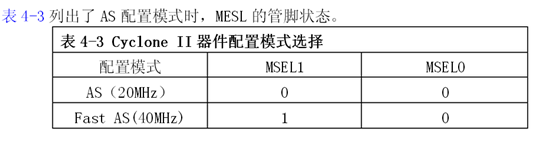

FPGA配置,调试方式:

1,官方pdf资料 704页 Configuration Handbook, Volume 1

,2,CYCLONE II系列配置手册

http://wenku.baidu.com/view/4b72cd768e9951e79b892704.html

http://wenku.baidu.com/view/ede221d376a20029bd642d61.html

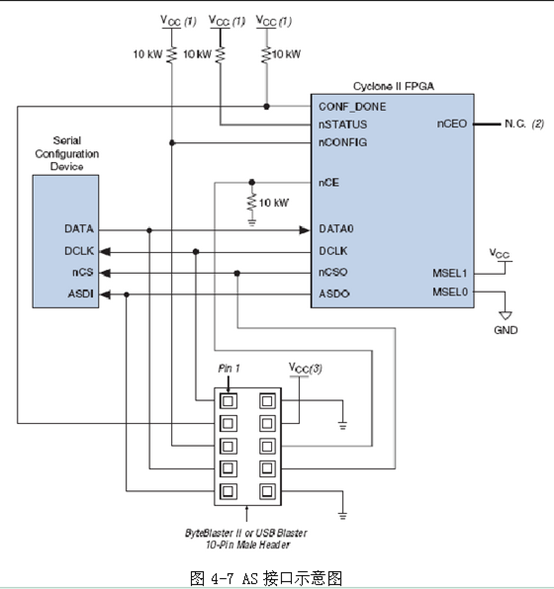

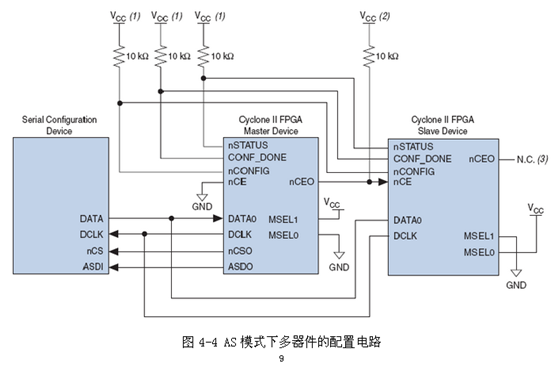

此处:nCE必须接到Gnd,或者拉低;

最小系统以及实现方案

参考资料

Cyclone II FPGA Starter Development Board Reference Manual

(mnl_cii_starter_board_rm.pdf)

Cyclone II FPGA Starter Development Kit P25-36048-00 User Guide

(ug_cii_starter_board.pdf)

PCI Development Kit, Cyclone II Edition Getting Started User Guide

(ug_cycloneII_pci_kit_gs.pdf)

EP3C25开发板官方原理图.pdf

http://wenku.baidu.com/view/14149ec3d5bbfd0a795673d7.html

另外网上也有很多开发板原理图可参考比如:

http://wenku.baidu.com/view/f5ad8b727fd5360cba1adb15.html

最小系统详细实现方案参考:

http://wenku.baidu.com/view/dc44866748d7c1c708a14524.html

参考教程:《FPGA应用开发入门与典型实例》 pdf 华清远见10年特献版.pdf

(很不错的参考资料!)

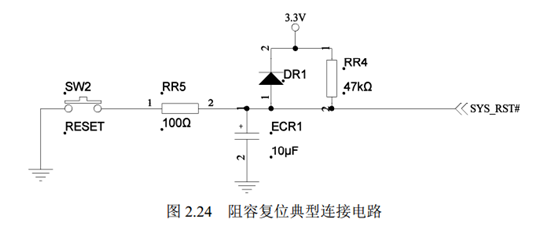

最小系统包括电源,LED指示灯,JTAG(AS),配置芯片,有源晶振,复位,特殊IO配置

关键点:FPGA的管脚主要包括:用户I/O(User I/O)、配置管脚、电源、时钟及特殊应用管脚等。其中有些管脚可有多种用途,所以在设计FPGA电路之前,需要认真的阅读相应FPGA的芯片手册。

---------配置管脚:

·MSEL[1..0]:用于选择配置模式。FPGA有多种配置模式,比如主动、被动、快速、正常、串行、并行等,可以此管脚进行选择。AS低速模式为两引脚为0 0

·DATA0:FPGA串行数据输入,连接至配置器件的串行数据输出管脚。

·DCLK:FPGA串行时钟输出,为配置器件提供串行时钟。

·nCSO(I/O):FPG**选信号输出,连接至配置器件的nCS管脚。

·ASDO(I/O):FPGA串行数据输出,连接至配置器件的ASDI管脚。

·nCEO:下载链器件使能输出。在一条下载链(Chain)中,当第一个器件配置完成后,此信号将使能下一个器件开始进行配置。下载链的最后一个器件的nCEO应悬空

nCE:下载链器件使能输入,连接至上一个器件的nCEO。下载链第一个器件的nCE接地。

·nCONFIG:用户模式配置起始信号上拉到3.3V。

·nSTATUS:配置状态信号上拉到3.3V。

·CONF_DONE:配置结束信号3.3V。

--------电源管脚:

VCCINT:内核电压。通常与FPGA芯片所采用的工艺有关,例如130nm工艺为1.5V,90nm工艺为1.2V。

·VCCIO:端口电压。一般为3.3V,还可以支持选择多种电压,如5V、1.8V、1.5V等。

·VREF:参考电压。

·GND:信号地。

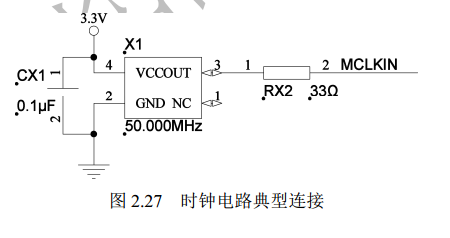

--------时钟和复位:

VCC_PLL:锁相环管脚电压,直接连VCCIO。

·VCCA_PLL:锁相环模拟电压,一般通过滤波器接到VCCINT上。

·GNDA_PLL:锁相环模拟地。

·GNDD_PLL:锁相环数字地。

·CLKnum(LVDSCLKnump):锁相环时钟输入。支持LVDS时钟输入,p接正端,num表示PLL序号。

·CLKnum(LVDSCLKnumn):锁相环时钟输入。支持LVDS时钟输入,n接负端,num表示PLL序号。

·PLLnum_OUTp(I/O):锁相环时钟输出。支持LVDS时钟输入,p接正端,num表示PLL序号。

·PLLnum_OUTn(I/O):锁相环时钟输出。支持LVDS时钟输入,n接负端,num表示PLL序号。

另外,FPGA的管脚中,有一些是全局时钟,这些管脚在FPGA中已经做好了时钟树。使用这些管脚作为

关键时钟或信号的布线可以获得最佳性能。

--------特殊管脚:

·VCCPD:用于选择驱动电压。

·VCCSEL:用于控制配置管脚和锁相环相关的输入缓冲电压。

·PORSEL:上电复位选项。

·NIOPULLUP:用于控制配置时所使用的用户I/O的内部上拉电阻是否工作。

·TEMPDIODEn/p:用于关联温度敏感二极管。

配置和调试接口(前面已经描述过):

可参考:http://wenku.baidu.com/view/ede221d376a20029bd642d61.html

http://wenku.baidu.com/view/4b72cd768e9951e79b892704.html

PCB<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

FPGA的PCB封装网上都可以找得到

an353_CN-smt建议.pdf

另外注意高速PCB布局布线的原则和技巧

最后附上连个不错的问答资料

cycloneII 经典问答

http://www.docin.com/p-371392629.html

FPGA经典100问

http://bbs.ednchina.com/BLOG_ARTICLE_3012305.HTM

(本文没涉及LVDS和NIOSII) 更多资料可到altera官网获取

用户1851850 2016-4-10 20:50

用户593939 2015-7-8 22:43

用户377235 2015-6-9 14:36

用户1838895 2015-5-28 10:43

hzddyx_297768481 2015-5-25 15:54

sunyzz 2015-5-21 20:55

用户610386 2015-5-21 13:55

liang890319_284707880 2013-9-9 17:10

用户403664 2013-9-9 14:59