数字式LCR测量仪

摘 要

本文设计了一个基于MSP430F5438A的低功耗RLC参数自动测试仪,采用数字电桥测量方法测量电阻、电容、电感值及电容电感的D值和Q值。该系统由自制电源模块、基准信号源、前端测量电路、相敏检波电路、键盘、12864液晶显示、FPGA、MSP430F5438A小系统等组成。其中,基准信号源用FPGA采用直接数字频率合成器(DDS)技术,产生较为精确的信号。前端测量电路采用半桥测量,由四级标准电阻和高精度仪器仪表放大器构成,能够自动选择相应的标准电阻和放大倍数进行测量,完成自动量程转换功能。另外,相敏检波电路利用DAC输出等于Vref与输入数字相乘的特性,完成矢量电压虚、实部的电压值转换。最后结合MSP430单片机控制和键盘、液晶显示,完成人机界面操作。

由于使用的是FPGA来产生正弦激励信号,具有较高的频率分辨率,比较好的完成频率切换并且能在频率改变时保持相位的连续。采用高速、低功耗的MSP430F5438A单片机完成自动切换量程和放大倍数的控制及最后的处理数据,使测量结果精确稳定。

关键词:FPGA、MSP430F5438A、数字电桥、相敏检波、12864液晶显示、按键

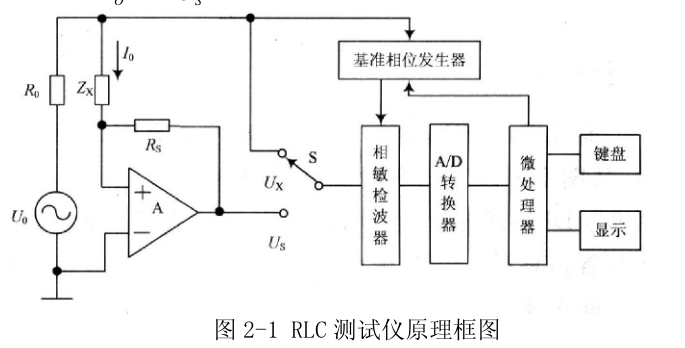

系统方框图如图1

1、谐振法:谐振法是由555定时器构成RC多谐振荡器产生脉冲波,是通过测量脉冲频率,根据频率和RC的关系,由测得的频率换算出被测电容电阻的大小。但是,该方案没有信号源部分,不满足提高要求,其次,电路的稳定性不够好,由于频率的不固定,测试时会带来很大误差,较难提高精度,而且不能测量电容电感的损耗系数和品质因数,不满足题目的要求。

2、交流电桥法:该方法具有较高的测量精度,但是该方法测量需要反复进行平衡调节,测量时间长,电路调整复杂,且不便于自动化测量。

3、伏安法:伏安法有固定轴法和自由轴法两种,区别在于相敏检波器的相位参考基准选取的不同。实际上,相敏检波的相位参考基准代表坐标轴的方向,相敏检波器的输出就是待测电压在坐标轴方向上的投影。根据要求,我们选择该方法。

由系统框图可知,被测阻抗

,由这式可知,只要测出Ux,Us在直角坐标系中两坐标轴X,Y上的投影分量,经过四则运算,即可求出测量结果.

被测信号与相位参考基准信号经过相敏检波器后,输出就是被测信号在坐标轴上的投影分量。相位参考基准代表着坐标轴的方向,为了得到每一个被测电压(Ux或Us)在坐标轴上的投影分量,基准相位发生器需要提供两个相位相差90度的相位参考基准信号。而自由轴法中,相位参考基准与Us没有确定关系,可以任意选择,即X,Y坐标轴可以任意选择,只需要保持两坐标轴准确正交90度。

通过模拟开关S选择某一被测量(如Ux或Us),基准相位发生器依次送出两个相位相差90度的相位参考基准信号,经相敏检波器后分别得到Ux或Us在两坐标轴上的投影分量Ux0,Ux90,Us0,Us90,各投影分量经A/D转换器可得对应的数字量,再经微处理器计算便得到测量元件参数值。

以下以电容串联电路的测量为例,推导出RLC参数的数学模型。

Ux=Ux0+jUx90

Us=Us0+jUs90

即:

所以:

同理,可推导出R,L的计算公式以及Qx的值。

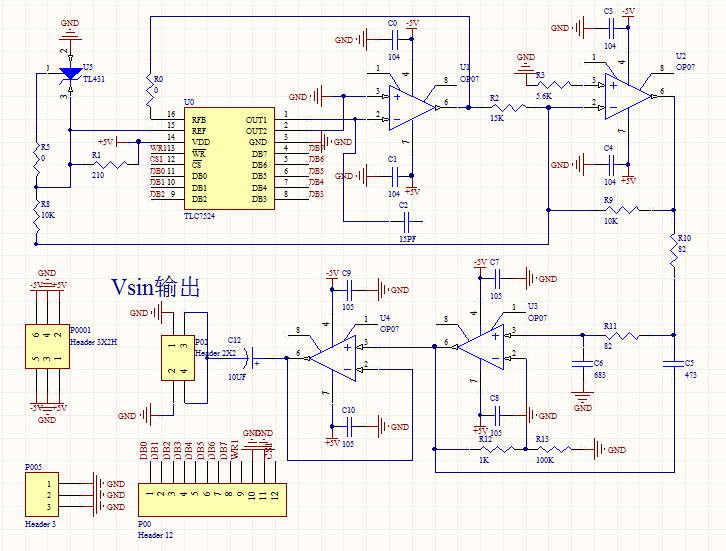

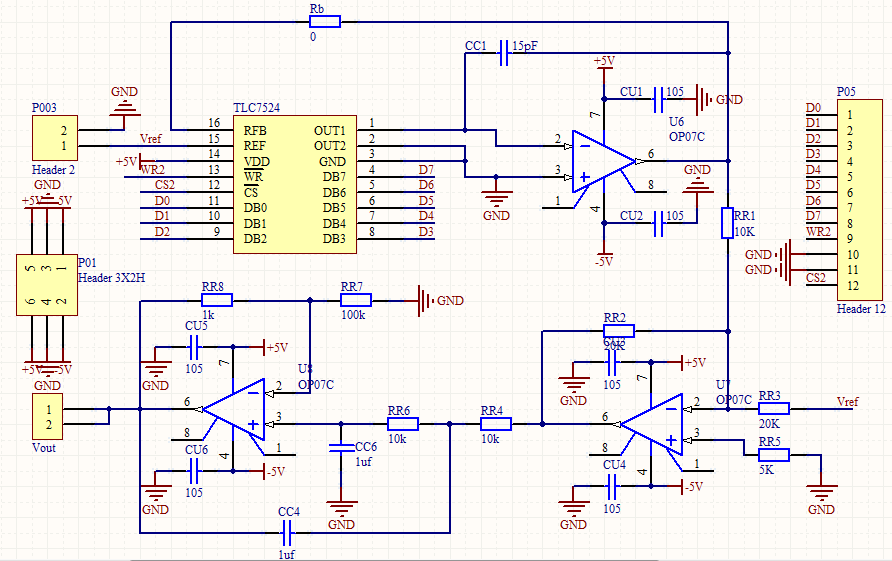

如上图所示,FPGA输出的波形数据经过数/模转换器AD7524进行数/模转换,AD7524是一种高速电流输出型的转换器,其典型的电流建立时间为0.1us,能够输出10KHz的要求。由FPGA输出的波形数据经AD7524和两片OP07实现双极性的模拟信号出。

2 .前端测量和放大倍数选择电路:

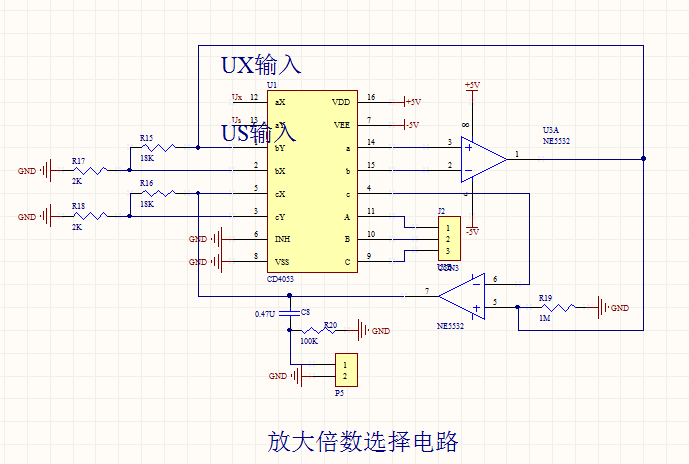

测量时,先通过模拟开关CD4053控制选通Ux或Us,并选择放大倍数,然后根据第一次的测量结果,判断该被测件应该适合哪个量程,然后再通过选通CD4052,选择合适的标称电阻,再进行正式测量。只有这样,出来的Ux和Us值才不会因为标称电阻的缘故出现太大而增大误差。

3.准数字相敏检波电路:

相敏检波器采用准数字相敏检波器,电路如上图所示,该电路主要完成矢量电压虚、实部电压值的转换。被测信号经过前端电路处理后,接到AD7524的Vref端,D0到D7是FPGA输出的与基准信号同步且正交的波形数据,这样就可以在产生基准信号的同时也产生了同频率的正交信号,利用了DAC输入数字与Vref相乘的特性,实现了准数字全波鉴相。

软件部分由FPGA和MSP430F5438A 两部分组成,其中FPGA实现DDS信号发生器,为前端测量电路提供激励信号,MSP430F5438A 实现自动切换量程,放大倍数控制,FPGA的信号频率和相位控制,按键和液晶显示控制,以及各种数据计算处理。

软件设计流程图如下:

FPGA模块:

FPGA作为控制产生基准正弦信号发生器和准数字相敏检波的控制模块,主要是产生两路正弦波,一路作为基准信号,另一路用于准数字相敏检波器,其原理框图如下图:

MSP430F5438A模块:

控制FPGA的输出相应频率和相位,由单片机控制智能切换量程,以获得比较精确的数据,并对相敏检波后的电压进行放大倍数控制,降低AD电压采集的困难和数据的稳定,控制按键,实现人机操作,并实现数据的运算处理,将数据显示在液晶上。

测试用仪器:双通道示波器 ,数字示波器,RLC测量仪表,单片机最小系统,函数信号发生器,FPGA系统板等。

测试时,先连接好电路图,然后在相应的位置处插入要测量的参数,从液晶显示上读取相应的数值。用RLC测量仪表测量该测量物,记录所得数据。将上述所得的两者数据进行比较,算出误差的大小。

|

标值 |

实际R值 |

测量R值 |

误差 |

|

10Ω |

9.9356 |

9.934 |

-0.016% |

|

100Ω |

98.8639 |

99.045 |

0.183% |

|

220Ω |

217.722 |

218.388 |

0.306% |

|

510Ω |

510.193 |

511.94 |

0.342% |

|

1000Ω |

990.89 |

990.763 |

-0.013% |

|

10KΩ |

9.937 |

9.939 |

0.020% |

|

51KΩ |

49.8463 |

49.656 |

-0.382% |

|

100KΩ |

101.22 |

101.277 |

0.056% |

|

510KΩ |

506.816 |

505.674 |

-0.225% |

|

1MΩ |

1.00788 |

1.000361 |

-0.746% |

|

5.1MΩ |

4.97661 |

4.989 |

0.249% |

|

10MΩ |

10.072 |

9.992 |

-0.794% |

|

标值 |

实际C值 |

测量C值 |

误差 |

实际D值 |

测量D值 |

误差 |

|

10PF |

10.055 |

10.16 |

1.044% |

0.00512 |

0.00338 |

-33.984% |

|

100PF |

104.408 |

103.85 |

-0.534% |

0.00211 |

0.00197 |

-6.635% |

|

1000PF |

1044 |

1036 |

-0.766% |

0.0088 |

0.00881 |

0.114% |

|

10nF |

10.256 |

10.259 |

0.029% |

0.0052 |

0.00513 |

-1.346% |

|

100nF |

94.422 |

94.403 |

-0.020% |

0.0055 |

0.0056 |

1.818% |

|

1UF |

1.0156 |

1.01477 |

-0.082% |

0.0026 |

0.00256 |

-1.538% |

|

10UF |

9.7914 |

9.78618 |

-0.053% |

0.039 |

0.03689 |

-5.410% |

|

33UF |

32.13 |

31.993 |

-0.426% |

0.072 |

0.07324 |

1.722% |

|

100UF |

96.211 |

96.232 |

0.022% |

0.0884 |

0.08885 |

0.509% |

|

220UF |

192.266 |

196.053 |

1.970% |

0.09295 |

0.09212 |

-0.893% |

|

470UF |

448.58 |

451.861 |

0.731% |

0.11134 |

0.10632 |

-4.509% |

|

标值 |

实际L值 |

测量L值 |

误差 |

实际Q值 |

测量Q值 |

误差 |

|

10uH |

9.8448 |

9.776 |

-0.699% |

1.13 |

1.1044 |

-2.265% |

|

20uH |

21.7385 |

21.582 |

-0.720% |

1.88 |

2.02497 |

7.711% |

|

100uH |

94.8051 |

94.864 |

0.062% |

3.2 |

2.887 |

-9.781% |

|

220uH |

192.94 |

194.636 |

0.879% |

2.09 |

2.2341 |

6.895% |

|

470uH |

454.72 |

455.594 |

0.192% |

0.52 |

0.54318 |

4.458% |

|

1mH |

989.35 |

984.756 |

-0.464% |

0.06 |

0.05906 |

-1.567% |

|

10mH |

10.728 |

10.589 |

-1.296% |

0.12 |

0.11862 |

-1.150% |

|

33mH |

33.485 |

33.282 |

-0.606% |

0.2 |

0.21035 |

5.175% |

|

100mH |

106.69 |

106.471 |

-0.205% |

0.31 |

0.31239 |

0.771% |

从所测数据看,电阻、电容、电感的测量精度达到基本要求和大部分发挥部分的要求。

经过团队的几天的不懈努力,终于将电阻电容电感简易测量仪制作完成,本设计完成了设计要求基本部分的全部要求,发挥部分绝大部分要求。整个装置测量可靠,稳定性好,使用FPGA制作DDS作为激励信号的产生,前端测量电路对测量信号选择合适的量程,并对信号进行放大滤波等处理,使得到的信号准确平稳,最后使用液晶显示,使显示更加明朗清晰。而自动切换量程又使得这个测量仪表具有较高的智能化水平。

参考文献

[1] 潘松,黄继业.EDA技术实用教程[M].北京:科学出版社,2002年

[2] 曾凡泰,陈美金.VHDL程序设计[M].北京:清华大大学学出版社,2001年

[3] 黄智伟.全国大学生电子设计竞赛训练教程[M].北京:电子工业出版式社,2005年

附录

附录1 键盘原理图

用户377235 2015-4-24 10:34

这个电路图使用什么软件画的

用户325709 2014-10-7 19:58

zhangqinguili_957239374 2012-12-1 16:52

用户380727 2012-11-30 13:15

zhangqinguili_957239374 2012-9-15 10:12

用户1707737 2012-9-15 09:58

zhangqinguili_957239374 2012-9-15 09:54

用户1707737 2012-9-15 09:44