我在编写一个十进制计数器时,遇到了使用assign与不用assign的情况,现在将两种情况分别讨论。

使用assign的情况:

代码:

module cnt10(

clk,rst_n,load,en,

datain,cout,dataout

);

input clk,rst_n,load,en;

input [3:0]datain;

output reg cout;

output [3:0] dataout;

reg [3:0]qout;

assign dataout = qout;

always @(posedge clk or negedge rst_n) begin

if(!rst_n) qout <= 0;

else if(en) begin

if(!load) qout <= datain;

else if(qout<9) qout <= qout+1'b1;

else qout <= 4'b0000;

end

end

always @(qout)

if(qout==9) cout <= 1'b1;

else cout <= 1'b0;

endmodule

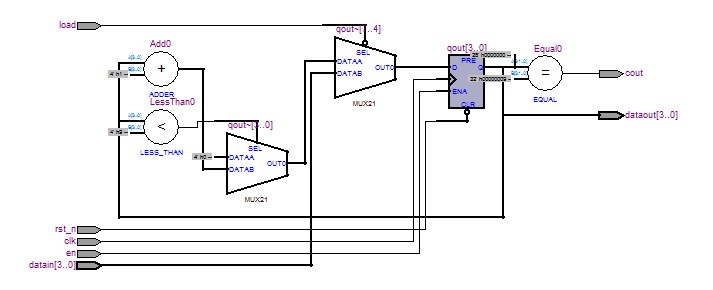

问题主要在RTL视图上:

不使用assign的情况:

代码:

module cnt10(

clk,rst_n,load,en,

datain,cout,dataout

);

input clk,rst_n,load,en;

input [3:0]datain;

output reg cout;

output reg[3:0] dataout;

always @(posedge clk or negedge rst_n) begin

if(!rst_n) dataout <= 0;

else if(en) begin

if(!load) dataout <= datain;

else if(dataout<9) dataout <= dataout+1'b1;

else dataout <= 4'b0000;

end

end

always @(dataout)

if(dataout==9) cout <= 1'b1;

else cout <= 1'b0;

endmodule

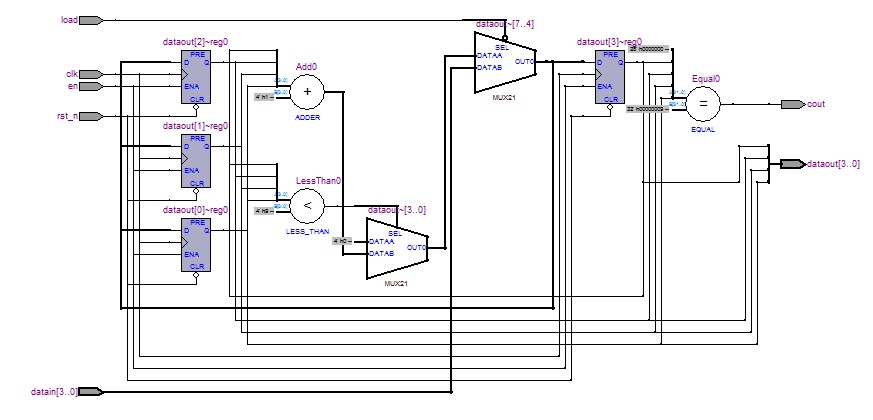

其RTL Viewer为:

可以看到,两者使用的器件基本上是一样的,但是其排版似乎有区别。使用assign的情况是把qout寄存器的内容输出给dataout,dataout是一个wire变量,换句话说就是一根导线;而不使用assign的情况,直接对dataout寄存器进行操作后了输出。看起来好像没什么区别,那么这两种用法到底哪种好?

/4

/4

文章评论(0条评论)

登录后参与讨论