FPGA器件密度提高到百万逻辑单元,设计团队需要实现更大更复杂的系统,并在更短的时间内满足越来越高的性能需求。相应的,FPGA设计面临着三个最为突出的问题,即:设计团队规模越来越大、需要花费很多时间来尝试重新使用其他人的设计、需要花费大量时间来进行验证。

为了应对不断增长的复杂性,如何切实可行地提升设计效能成为业界共同探索的一个问题。Altera亚太区产品市场经理解晓东介绍,提高设计抽象级即相当于提高了设计效能。随着器件容量的增加、设计复杂度的增加,设计抽象级从门级发展到了寄存器传送级(RTL),又向IP级、系统级演变,Altera的开发工具也从原理图输入向Quartus II综合、SoPC Builder进阶。如今,SoPC Builder的下一代产品Qsys更是以不可阻挡的姿态出现在业界。

Altera亚太区产品市场经理解晓东

Qsys系统集成工具是Quartus II开发软件的一部分,它采用业界首创的FPGA优化芯片网络技术,能够提供存储器映射和数据通路互联。相比其前身SOPC Builder,Qsys的性能几乎提高至两倍,同时支持业界标准IP接口,例如AMBA。Qsys将采用使用方便的SoPC Builder界面,支持与现有嵌入式系统移植的后向兼容。而且,这一高级互联技术将支持分层设计、渐进式编译以及部分重新配置方法。Qsys可提高设计抽象级,自动生成互联,使用标准接口,为设计人员大幅缩短了开发时间,增强了设计重用性。

攻克设计规模难题

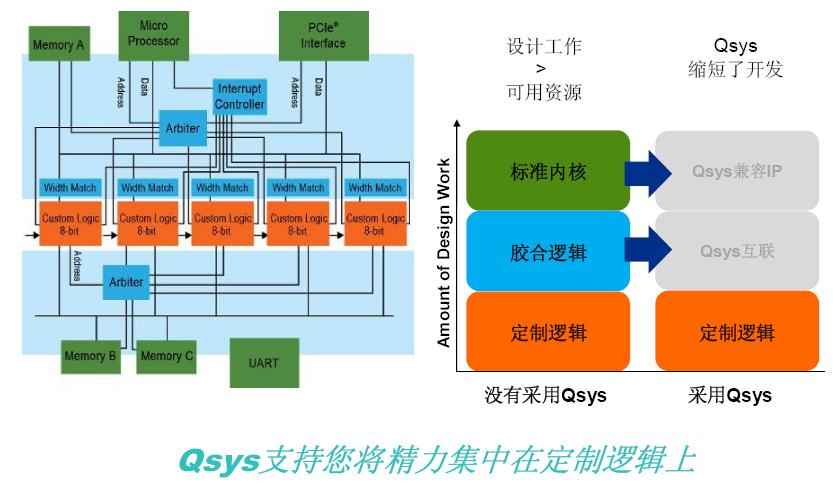

下图鲜明地展示了Qsys给系统设计带来的好处。图中绿色部分表示标准内核,是一个将标准IP进行组合的搭积木的过程。蓝色部分表示胶合逻辑,需要进行仲裁、中断控制、带宽匹配等工作。橙色部分则表示定制逻辑,它与标准模块不同,可根据设计需求进行差异化开发,许多拥有IP的公司最关心的正是这一部分的设计。在不使用Qsys的情况下,这三部分工作都需要进行匹配。但有了Qsys以后,它的兼容IP和互联特性可分担标准内核和胶合逻辑方面的工作,使设计人员将更多的精力集中在定制逻辑上,创造差异化的价值。

Qsys目前可提供超过一百个兼容IP,如:接口协议IP(PCIe、TSE)、存储器IP(DDR/DDR2/DDR3)、视频和图像处理(VIP)IP(VIP套装包括:缩放器、矩阵、去隔行器以及alpha混合合成器)、嵌入式IP(JTAG、UART、SPI、RS232)以及多种处理器IP。

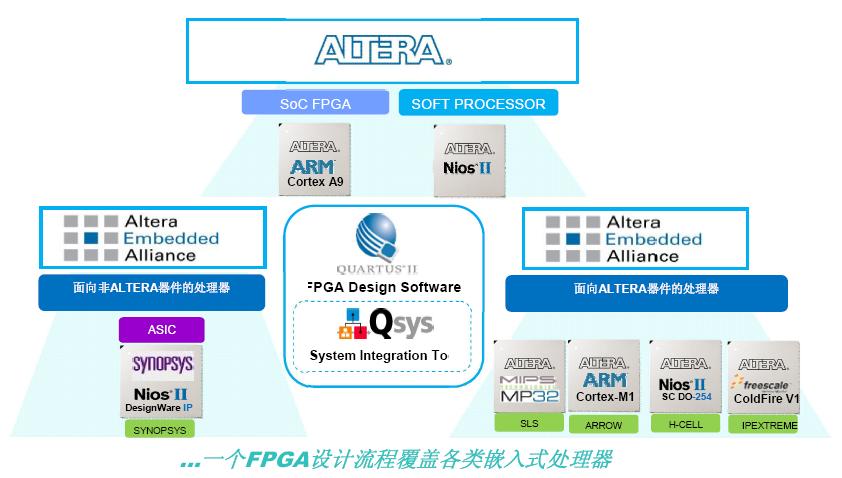

值得一提的是,Qsys几乎可支持所有常用的嵌入式处理器,例如基于ARM Cortex A9的SoC FPGA和基于Nios II的软核处理器,以及Altera嵌入式联盟所提供的其他处理器(如:MIPS MP32、ARM Cortex-M1、Nios II SC DO-254以及Freescale ColdFire V1等)。解晓东介绍,软核处理器可通过FPGA模拟CPU,其优点在于占用资源少,25K逻辑单元可放置几十个处理器,若用户对性能要求有差异,Altera软核有三档配置可满足不同需求。

此外,Qsys可完成自动集成任务,在运用标准IP加速开发的同时,其GUI界面支持快速集成,避免了繁琐而又容易出错的集成任务。

攻克设计重用难题

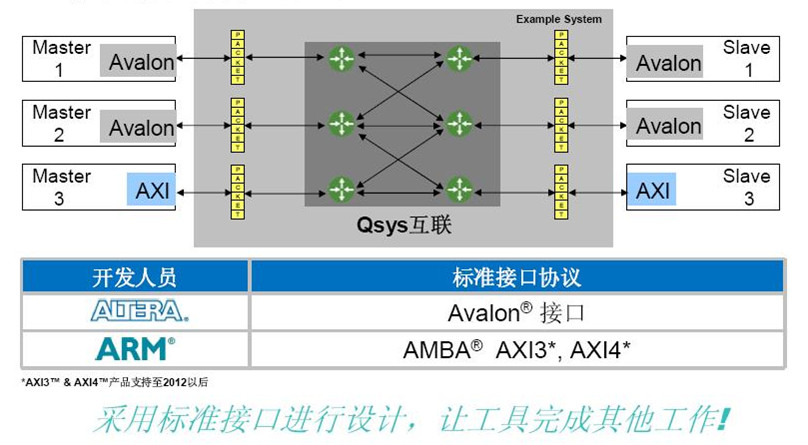

设计重用是提升效率的有效环节,但是它通常会导致以下问题:设计者需重新设计接口;设计者需对各种修改过的设计提供支持;在没有文档记录的情况下,其他人不得不搞清楚接口是怎样工作的。针对这些问题,Qsys进行了优化,其片上网络架构可完成无线接口的互连,它支持标准接口,例如Altera的Avalon接口、ARM的AMBA AXI接口,具有经过维护的可用的文档,用户不需进行重新设计接口的工作。解晓东强调,在设计重用方面,业界多数工具(包括SoPC Builder在内)只能做到IP级,而Qsys是唯一可做到子系统级别的工具。

设计重用的另一个特性是:在设计重复使用流程时,可将RTL设计导入Qsys,作为其中一个IP来用。通过将低层次的抽象设计放到高层次Qsys中,可将文本格式编写的代码引入Qsys,打包后生成接口,在标准库中生成设计模块,从而在设计中重用这些模块,整个过程是非常容易操作的图形化过程。解晓东补充,SoPC Builder是完全平铺式的设计流程,对于一些复杂的设计而言,界面拉得很长,不便于查找设计问题;而Qsys可将一些IP进行子系统打包,使设计更具层次性。这对于一些国际化的公司非常实用,便于他们在全球范围内共享设计,进行重用。

攻克验证难题

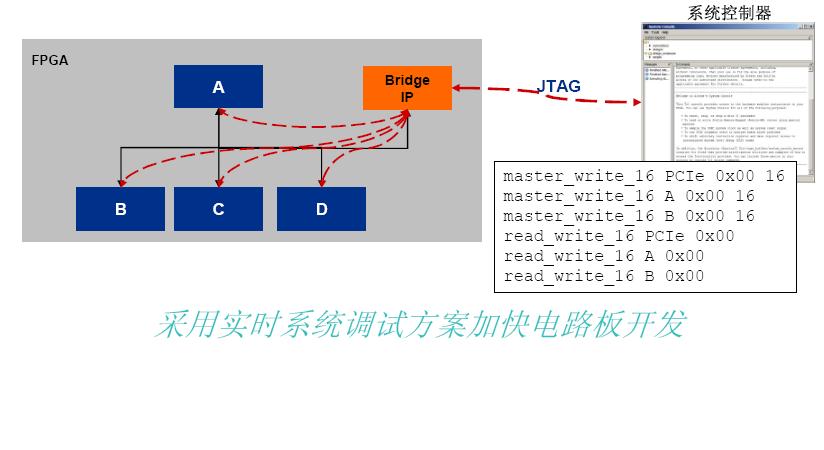

如果说设计过程是充满了创造力的愉悦享受,验证过程相比就乏味了很多。基于寄存器的调试需要逐个去查询寄存器,工作量非常庞大,也存在着很多的不确定性。Qsys采用了系统控制台的调试工具,去对地址位置进行读写操作,而非对每个寄存器都读写,通过在总线系统上读写可快速锁定问题出现在哪个模块,从而加快验证进程。此外,Qsys提供定制的、图形化的界面,方便易用,使调试过程不再枯燥。

亚太区Qsys研讨会巡回举行中

为帮助用户更快、更好地了解Qsys,今年3月至6月,Altera在亚太区15个城市巡回举办“采用Qsys实现系统集成研讨会”,通过技术演讲、技术演示、实践练习等方式,与会者可以观看基于Qsys的PCIe至DDR3设计演示,并通过实践练习来开发设计,体验Qsys如何大幅提升设计效能。这一研讨会已有超过200名工程师参加,现正接受网上注册。下图为在北京清华大学实验室的研讨会现场。

相关链接:

注册可点击

http://www.altera.com.cn/education/events/evt-qsys-workshop.html

关于Qsys系统集成工具,更多信息可访问http://www.altera.com.cn/products/software/quartus-ii/subscription-edition/qsys/qts-qsys.html

在FPGA系统设计上发挥芯片网络体系架构的优势(白皮书)http://www.altera.com.cn/literature/wp/wp-01149-noc-qsys_CN.pdf

SoPC Builder至Qsys移植指南

http://www.altera.com.cn/literature/an/an632.pdf

PCIe & DDR3参考设计

http://www.altera.com/support/refdesigns/ip/interface/ref-pciexpress-ddr3-sdram.html

/5

/5

文章评论(0条评论)

登录后参与讨论