Multi-Frequency Analysis 多频率分析

一些FPGA的设计当中会有多个时钟,而各个时钟的频率也会不同。

Clock Multiplexing 时钟多路传输

这部分介绍的约束命令是:create_clock 和 set_clock_groups

在时钟多路传输中,你可以从多个时钟里选择一个。Figure 1–7展示了一个典型的2:1时钟多路复用器(clock multiplexer) 约束

Example 1–9展示了约束命令 针对时钟多路复用器

Example 1–9. Clock Multiplexer Constraints

#Create the first input clock clkA to the mux

create_clock -period 10.000 -name clkA [get_ports {clkA}]

#Create the second input clock clkB to the mux

create_clock -period 20.000 -name clkB [get_ports {clkB}]

#Cut paths between clkA and clkB

set_clock_groups -exclusive -group { clkA} -group { clkB}

Externally Switched Clock 外部切换时钟

这部分介绍的约束命令是:create_clock 和 set_clock_groups

通过一个外部时钟复用器或跳钱设置(jumper setting),数字系统能对同一个时钟端口提供不同频率的时钟。Timequest analyzer 能够建模这种实例,通过使用create_clock约束命令和 -add选项。

Figure 1–8展示了一个简单的寄存器-寄存器路径,你可以使用100MHz或者50MHz的时钟来驱动其时钟端口

Example 1–10展示了对可切换外部时钟的约束

Example 1–10. Externally Switched Clock Constraints

# The clk port can be driven at 100MHz (10ns) or

# 50MHz (20ns)

# clkA is 10ns

create_clock \

-period 10.000 \

-name clkA \

[get_ports {clk}]

# clkB is 20ns assigned to the same port

# Requires -add option

create_clock \

-period 20.000 \

-name clkB \

[get_ports {clk}] \

-add

set_clock_groups \

-exclusive \

-group {clkA} \

-group {clkB}

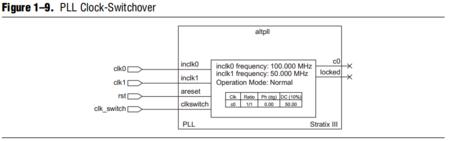

PLL Clock Switchover PLL时钟替换

这里描述了 derive_pll_clocks命令

PLL可以从两个输入时钟里选取一个 通过Altera FPGA里面的 PLL clock-switchover 输出(Figure 1–9).

Example 1–11 s展示了对PLL clocks switchover 的约束

Example 1–11. PLL Clock Switchover Constraints

#create a 10ns clock for clock port clk0

create_clock \

-period 10.000 \

-name clk0 \

[get_ports {clk0}]

#create a 20ns clock for clock port clk1

create_clock \

-period 20.000 \

-name clk1 \

[get_ports {clk1}]

#automatically create clocks for the PLL output clocks

#derive_pll_clocks automatically makes the proper

#clock assignments for clock-switchover

derive_pll_clocks

/5

/5

文章评论(0条评论)

登录后参与讨论