最近一个项目中,需要在xilinx v7690t的FPGA高速接口上挂载PCIEx8接口,基于此项目,和大家分享一下在xiinx FPGA上如何挂载PCIE接口。

首先,要在FPGA上挂载PCIE接口,必须明确的是挂载在GTH或GTX高速Bank上。而对于690t-fgg1927器件,有20个高速bank,分别为bank110-bak119和bank210-bank219,那么我们在硬件设计中,PCIE接口该接到哪个bank呢?

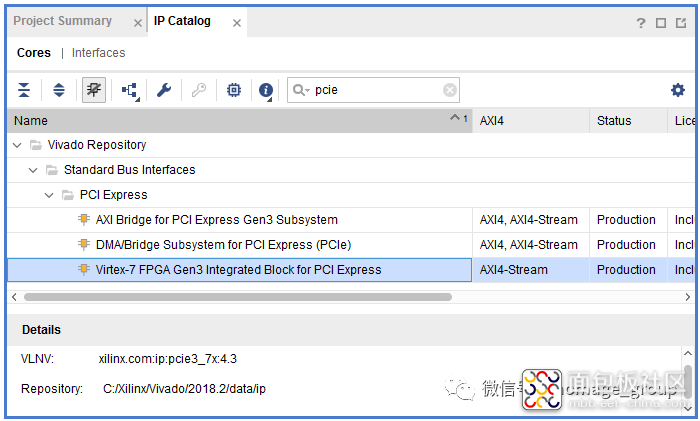

本项目中,我们需要的是PCIEx8接口,也就是说需要8通道高速收发器,而690t的每个高速bank只有4通道收发器,所以需要2个bank来实现。在硬件设计中,那么该接哪两个高速bank呢?不妨先从逻辑着手,打开vivado软件,搜索PCIE IP核,出现如下几个选项,我用的vivado软件版本为2018.2。

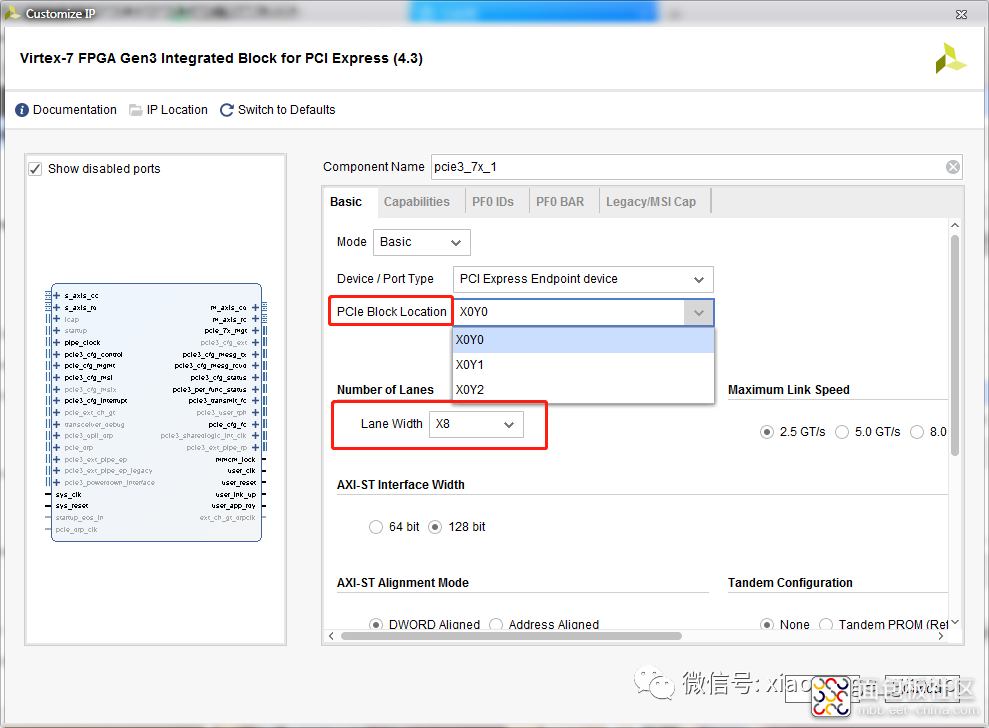

我们选择最后一个ip,双击之后显示界面如下。

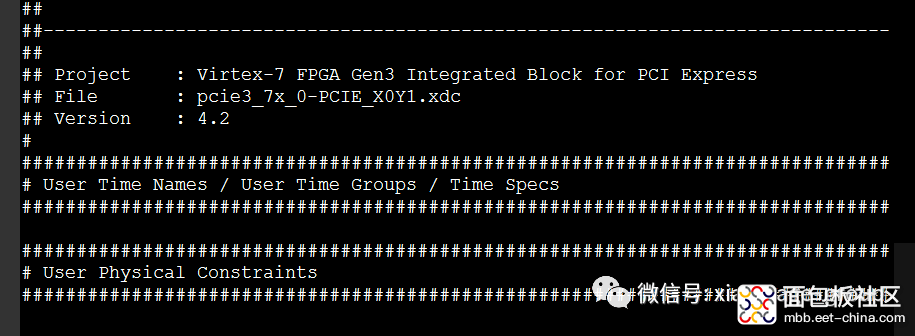

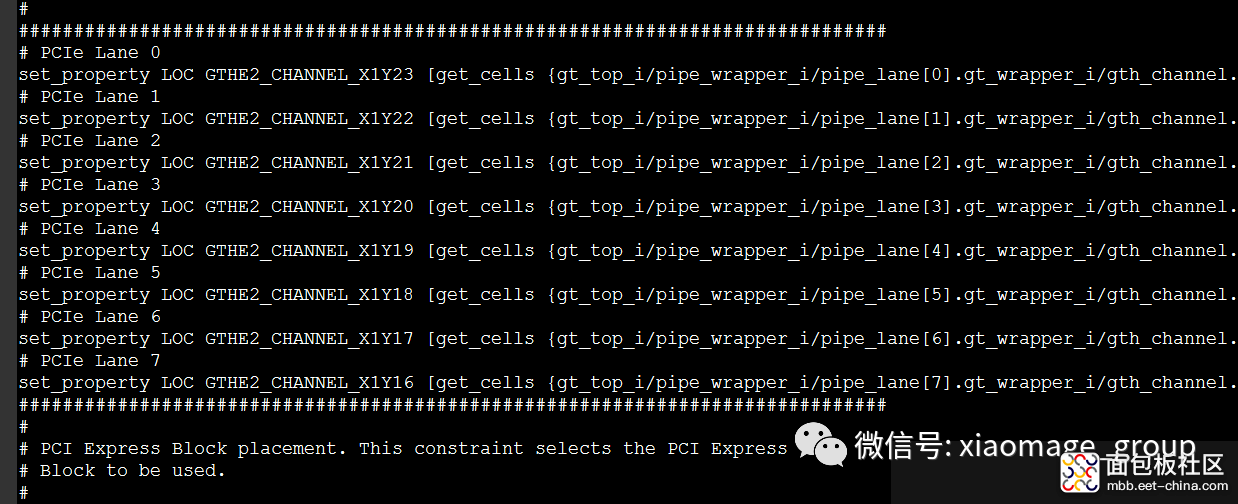

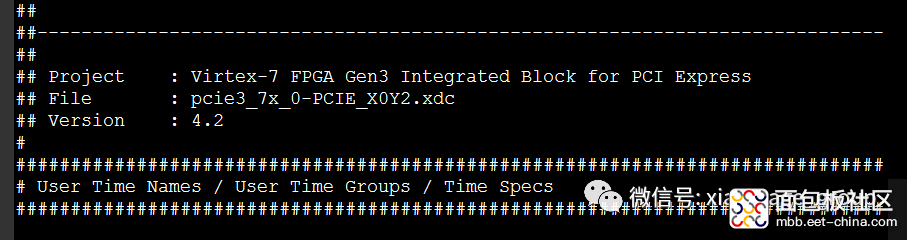

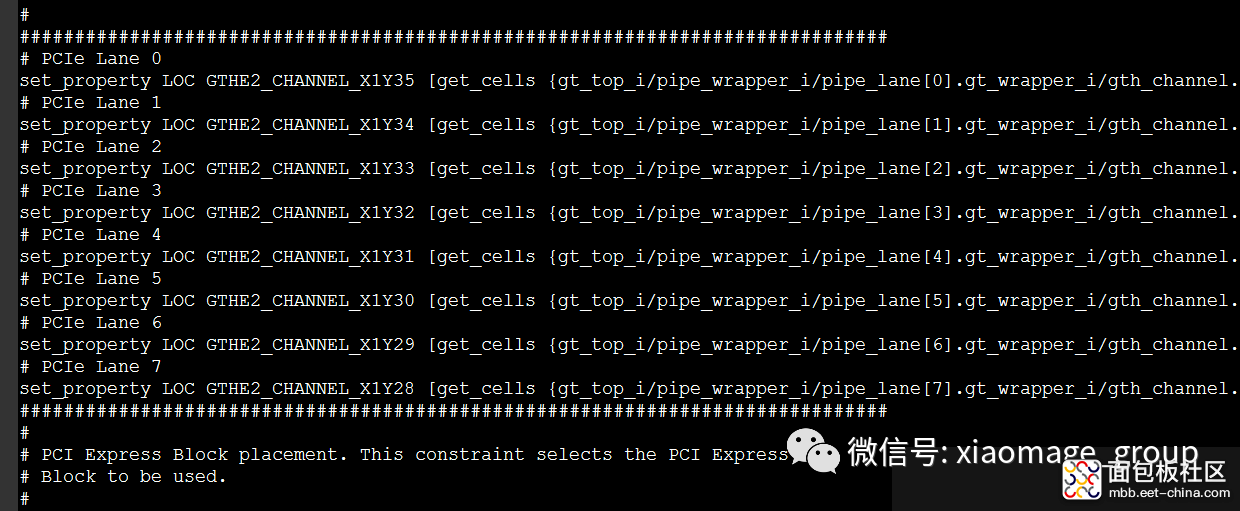

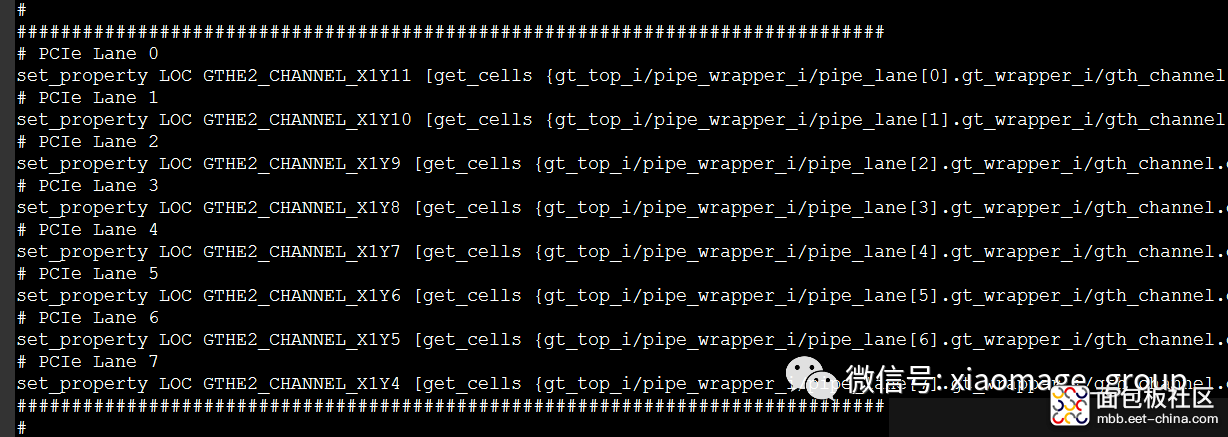

在该界面中,对于硬件设计而言,我们只关注两部分,分别是Lane Width和PCIe Block Locatin这两个参数,第一个参数为PCIe的通道数,也就是实际的PCIe x1,x2,x4,x8。第二个参数就是我们的PCIe高速接口在FPGA高速bank上的连接位置,该参数有三个选项,分别为X0Y0,X0Y1,X0Y2。每个选项对应着不同的单个或相邻的bank。以下是我分别选择三个选项,vivado自己生成的xdc文件。

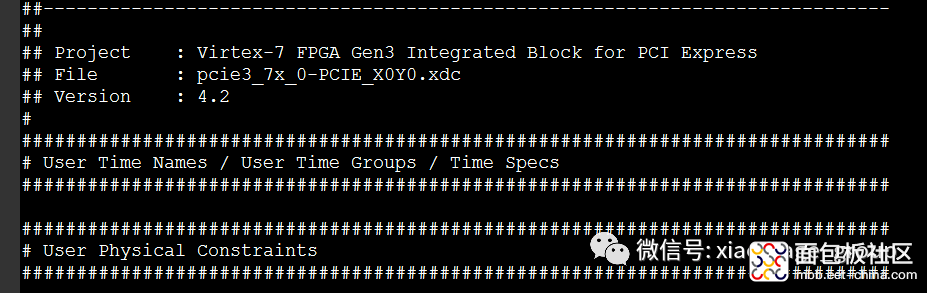

X0Y0:

X0Y1:

X0Y2:

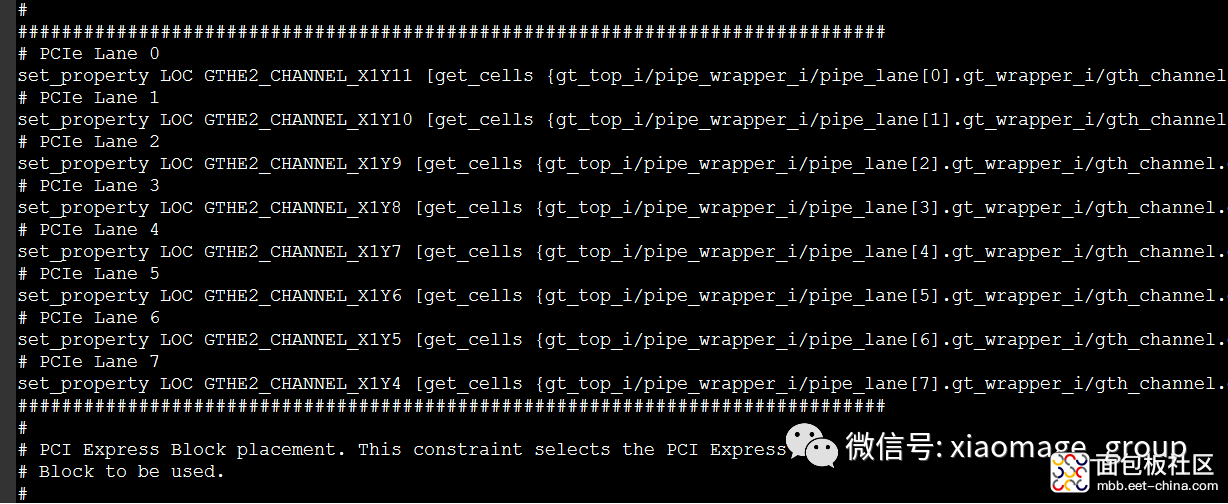

我们从上图中可以看出,无论我们选择三个选项中的哪一个,在xdc文件中,体现的只有X1Y4之类的约束,并没有像我们之前编写逻辑时约束的具体管脚号。那么我们怎么去查X1Y4这类约束对应的bank呢?这个时候我们需要去xilinx的官网查找GTX/GTH手册了。

在xilinx官网有一个ug476手册,在该手册中详细的描述了每一个location。

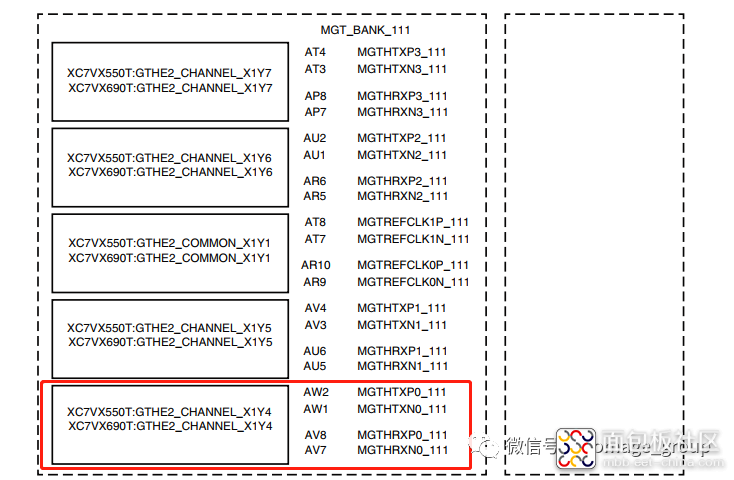

由于本次项目中使用的是v7690t-ffg1927器件,所以在ug476手册的416页到425页可以查到具体对应的bank。

例如之前生成的xdc文件中的X1Y4,对应的是bank111的AW2,AW1,AV8,AV7四个引脚。所以我们在IP配置界面选择PCIEx8选项,X0Y0时,此时8通道高速收发器对应的是bank111-bank112;选择PCIEx8选项,X0Y1时,此时8通道高速收发器对应的是bank114-bank115;选择PCIEx8选项,X0Y2时,此时8通道高速收发器对应的是bank117-bank118。

通过以上查找分析,我们确定了当使用PCIEx8高速接口时,具体应该连接到了那两个bank,那么8通道差分收发器在这两个bank上怎么连接呢?例如我们选择了bank111-bank112,lan0-lan7是从bank111的MGTHT/RXP/N0开始到bank112的MGTHT/RXP/N3正向连接呢还是逆向呢?其实从前面生成的xdc文件我们可以看出,选择X0Y0时,对应的bank为bank111-bank112。

我们可以看出Lane0对应的是X1Y11,也就是bank112的MGTHT/RXP/N3差分对儿,而Lane7对应的是X1Y4,也就是bank111的MGTHT/RXP/N0CH差分对儿。所以在官方推荐中,是逆序引脚连接,也就是PCIE_T/RXD_0_P/N连接至bank112的MGTHT/RXP/N3,依次递减,PCIE_T/RXD_7_P/N连接至bank111的MGTHT/RXP/N0。

那么如果在硬件设计中,我们的引脚是正序连接的,PCIE_T/RXD_0_P/N连接至bank111的MGTHT/RXP/N0,依次递增,PCIE_T/RXD_7_P/N连接至bank112的MGTHT/RXP/N3,该怎么办,此时只需修改IP生产的xdc文件,把对应的Lane改成对应的Location即可。

通过以上分析理解,我们知道了在硬件设计中,xilinx FPGA的V7690T-FGG1927器件如何连接高速PCIEx8接口。如有理解不到位的地方,还请各位大佬不吝指导。

关注小编的微信公众号查看更详细的内容哟:xiaomage_group。

作者: 小马哥电子, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-1761950.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/5

/5

小马哥电子 2021-10-9 13:40

jieranerabc 2021-7-9 10:00