module block;

reg timer_clk;

initial

begin

timer_clk = #5 1;

timer_clk = #4 0;

timer_clk = #6 1;

timer_clk = #8 0;

timer_clk = #10 1;

end

endmodule

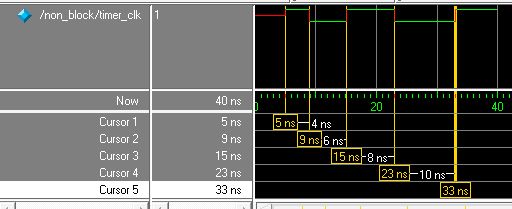

从波形中可以看出,对timer_clk的赋值是顺序执行的,总赋值时间用了33ns。

执行顺序是一条赋值结束后,经过延时再执行另一条赋值。

总结:顺序逐条执行

module non_block;

reg timer_clk;

initial

begin

timer_clk <= #5 1;

timer_clk <= #4 0;

timer_clk <= #6 1;

timer_clk <= #8 0;

timer_clk <= #10 1;

end

endmodule

非阻塞是如果没有内部传输延时,右侧的赋值将同时赋值给左侧。

这里每次赋值前加入了内部延时,使得赋值在时间上有了不同。总体时间用了10ns。

总结:先算好<=右侧,最后同时赋值给<=左侧。

/5

/5

文章评论(0条评论)

登录后参与讨论