分频就是用一个时钟信号通过一定的电路结构变成不同频率的时钟信号,这里介绍一下整数分频电路的设计方法。整数分频电路有偶数分频和奇数分频两种,我们以实现占空比为50%的分频电路为例子来解释一下分频电路设计的基本原理。假设时钟周期为T,则二分频后输出的时钟周期为2T,三分频后输出的时钟周期为3T,N分频后输出的时钟周期为NT,这是设计分析的基本思路。

1.偶数分频实现

二分频电路设计

二分频电路的实现是最为简单的,只需要用一个D触发器便能实现,因为D触发的输出值每隔一个输入时钟周期T才更新一次值,所以我们只要每次D触发器寄存值的时候把它的输出值取反就可以了,这样它的高电平持续时间为T,低电平持续时间也为T,则为二分频。具体的代码如下所示。

-

module clkdiv(clk,rst_n,clk_2);

-

input clk,rst_n;

-

output clk_2;

-

reg q;

-

-

always @(posedge clk or negedge rst_n)

-

if(!rst_n)

-

q<=1'b0;

-

else

-

q<=~q;

-

-

assign clk_2=q;

-

endmodule

这个设计非常简单,不作过多解释。

六分频电路设计

按照设计的思路,六分频总的时钟周期应该为6T,高电平持续时间为3T,低电平持续时间为3T,我们只需要用一个0-5的计数器,计数从0到5一直循环,当计数器为0,1,2时,输出高电平,计数器为3,4,5时,输出低电平。

具体代码实现如下

-

module clkdiv6(clk,rst_n,clk_2);

-

input clk,rst_n;

-

output clk_2;

-

reg [2:0] q; //因为用到0-5的计数器,一共要3位D触发器

-

reg clk_2;

-

always @(posedge clk or negedge rst_n)

-

if (!rst_n)

-

q<=3'd0;

-

else if(q==3'd5)

-

q<=3'd0;

-

else

-

q<=q+1'b1;

-

-

always @(posedge clk or negedge rst_n)

-

if(!rst_n)

-

clk_2<=1'b0;

-

else if(q<3'd3)

-

clk_2<=1'b1;

-

else

-

clk_2<=1'b0;

-

endmodule

经过仿真,符合六分频的设计思路,占空比也为50%,3T的时间为高电平,3T的时间为低电平。

2N分频电路设计思路

偶数分频电路的基本实现思路就是利用计数器,利用0-(2N-1)的计数器,当计数器计数在0-(N-1)的时候输出高电平,其余时间输出低电平就可以完成占空比50%的2N分频电路了

2.奇数分频实现

三分频电路实现

三分频的电路如果按照偶数分频的思想来设计就会遇到一个难题,因为是奇数,不能做到计数器计数到一半的时候输出取反,也就是说按照偶数分频的思路做不到占空比50%,在这里要换一个思路来设计。我们仍然分析一下三分频电路的特点,三分频电路的周期为3T,高电平持续时间为1.5T,低电平持续时间也为1.5T。假设用上面的思路,用1个计数器来分频,则也可以得到三分频,但是占空比为66.7%,即高电平持续时间为2T,低电平持续时间为1T。以下为占空比50%的三分频电路实现,用2个三进制计数器,第1个为时钟上升沿触发,第2个为时钟下降沿触发。对第1个计数器而言,小于2取高电平则,0-2T为高电平,2T-3T为低电平,对第2个计数器而言,小于2取高电平,则0.5T-2.5T为高电平,2.5T-3.5T为低电平,实质上第2个的波形延时了0.5T,他们公共的取高电平的时间为0.5T-2T,刚好是1.5T,正式三分频占空比为50%高电平所持续的时间。下面为具体代码实现。

-

module clkdiv3(clk,rst_n,clk_2);

-

input clk,rst_n;

-

output clk_2;

-

reg [1:0]count1;//上升沿触发的3进制计数器1

-

reg [1:0]count2;//下降沿触发的3进制计数器2

-

reg clk_p,clk_n;

-

always @(posedge clk or negedge rst_n)//上升沿触发的3进制计数器1

-

if(!rst_n)

-

count1<=2'd0;

-

else if(count1==2'd2)

-

count1<=1'b0;

-

else

-

count1<=count1+1'b1;

-

always @(posedge clk or negedge rst_n)

-

if(!rst_n)

-

clk_p<=1'b0;

-

else if(count1<2'd2)

-

clk_p<=1'b1;

-

else

-

clk_p<=1'b0;

-

always @(negedge clk or negedge rst_n)//下降沿触发的3进制计数器2

-

if(!rst_n)

-

count2<=2'd0;

-

else if(count2==2'd2)

-

count2<=2'd0;

-

else

-

count2<=count2+1'b1;

-

always @(negedge clk or negedge rst_n)

-

if(!rst_n)

-

clk_n<=1'b0;

-

else if (count2<2'd2)

-

clk_n<=1'b1;

-

else

-

clk_n<=1'b0;

-

assign clk_2=clk_p&clk_n;

-

endmodule

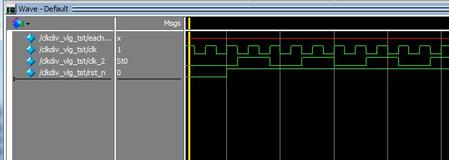

仿真的波形图如下

可见,实现了三分频占空比为50%的功能,但是仍然有不足的地方就是相位不是和原始时钟同相,延迟了0.5T。

五分频电路设计

按照三分频的分频思路,五分频的代码如下

-

module clkdiv5(clk,rst_n,clk_2);

-

input clk,rst_n;

-

output clk_2;

-

reg [2:0]count1;//上升沿触发的5进制计数器1

-

reg [2:0]count2;//下降沿触发的5进制计数器2

-

reg clk_p,clk_n;

-

always @(posedge clk or negedge rst_n)//上升沿触发的5进制计数器1

-

if(!rst_n)

-

count1<=3'd0;

-

else if(count1==3'd4)

-

count1<=1'b0;

-

else

-

count1<=count1+1'b1;

-

always @(posedge clk or negedge rst_n)

-

if(!rst_n)

-

clk_p<=1'b0;

-

else if(count1<5'd4)

-

clk_p<=1'b1;

-

else

-

clk_p<=1'b0;

-

always @(negedge clk or negedge rst_n)//下降沿触发的5进制计数器2

-

if(!rst_n)

-

count2<=3'd0;

-

else if(count2==3'd4)

-

count2<=3'd0;

-

else

-

count2<=count2+1'b1;

-

always @(negedge clk or negedge rst_n)

-

if(!rst_n)

-

clk_n<=1'b0;

-

else if (count2<3'd4)

-

clk_n<=1'b1;

-

else

-

clk_n<=1'b0;

-

assign clk_2=clk_p&clk_n;

-

endmodule

设计的思路和三分频一样,只是把计数器的进制改动了,并且把翻转时的判断逻辑改动了。

总结

按照以上偶数分频和奇数分频的方法,可以设计任意的N分频电路,以获得占空比为50%的时钟,不足之处是奇数分频不能获得与时钟同相的波形。

/5

/5

用户1722105 2015-12-31 14:53

用户1847540 2015-12-21 10:42

用户402158 2015-11-4 16:22