// 74ls138.v

module decoder_38( //input

d_in,

e1,

e2a_n,

e2b_n,

//output

data_out

);

input [2:0] d_in; //38译码器输入端(A2, A1, A0)

input e1; //38译码器选通端

input e2a_n; //38译码器选通端

input e2b_n; //38译码器选通端

output [7:0] data_out; //38译码器输出端

reg [7:0] data_out;

//******************************************************************************

// 模块名称:38译码器模块

// 功能描述:完成38译码器的功能

//******************************************************************************

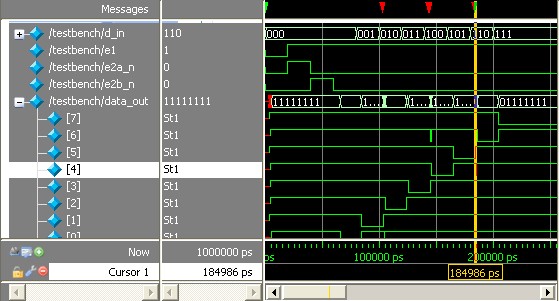

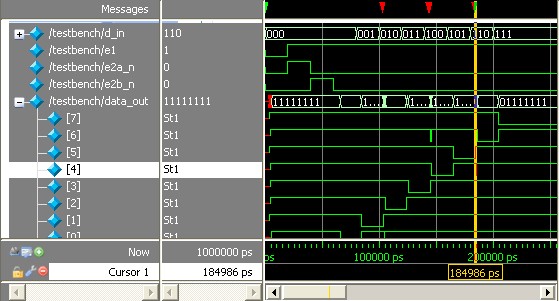

always@(d_in, e1, e2a_n, e2b_n)

begin

if (e1 ==0 || e2a_n == 1 || e2b_n == 1) //选通端无效

data_out = 8'b1111_1111;

else

begin

case(d_in)

3'b000:

data_out = 8'b1111_1110;

3'b001:

data_out = 8'b1111_1101;

3'b010:

data_out = 8'b1111_1011;

3'b011:

data_out = 8'b1111_0111;

3'b100:

data_out = 8'b1110_1111;

3'b101:

data_out = 8'b1101_1111;

3'b110:

data_out = 8'b1011_1111;

3'b111:

data_out = 8'b0111_1111;

endcase

end

end

endmodule

// testbench.v

`timescale 1ns/1ns

module testbench;

reg [2:0] d_in;

reg e1, e2a_n, e2b_n;

wire [7:0] data_out;

decoder_38 decoder_38_0(

.d_in(d_in),

.e1(e1),

.e2a_n(e2a_n),

.e2b_n(e2b_n),

.data_out(data_out)

);

initial

begin

d_in = 3'b000; e1=0; e2a_n = 0; e2b_n = 0;

#20 e1 = 1; e2a_n = 1;

#20 e2a_n = 0; e2b_n = 1;

#20 e2b_n = 0;

#20 d_in = 3'b001;

#20 d_in = 3'b010;

#20 d_in = 3'b011;

#20 d_in = 3'b100;

#20 d_in = 3'b101;

#20 d_in = 3'b110;

#20 d_in = 3'b111;

end

endmodule

/4

/4

文章评论(0条评论)

登录后参与讨论