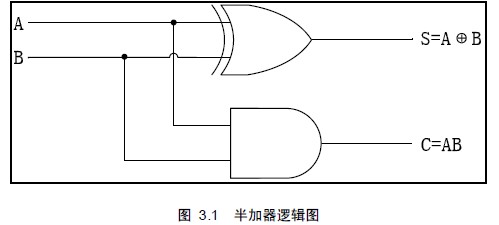

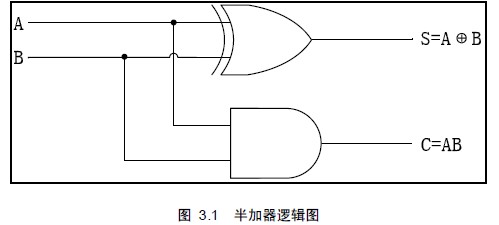

// half_adder.v

module half_adder(

A, //输入选择地址由开关决定,0:按下,1:未按下

B, //输入选择地址由开关决定,0:按下,1:未按下

S, //输出,0:点亮,1:熄灭

C //输出,0:点亮,1:熄灭

);

input A;

input B;

output S;

output C;

assign S = A^B;

assign C = A&B;

endmodule

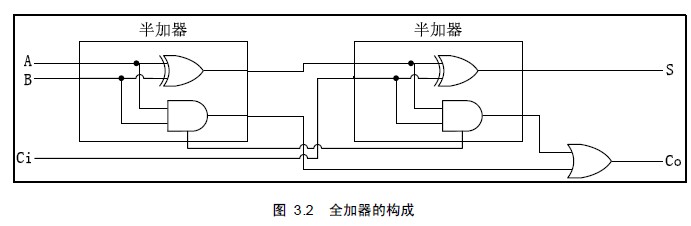

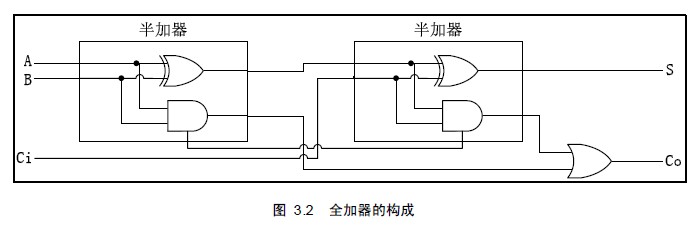

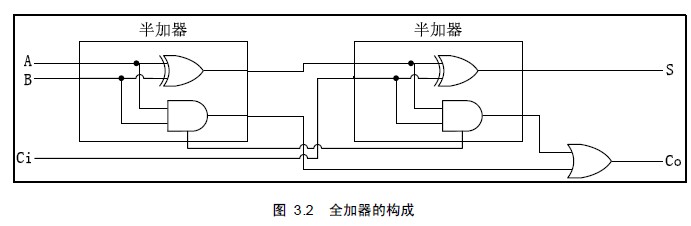

// full_adder.v

module full_adder(

A, //输入选择地址由开关决定,0:按下,1:未按下

B, //输入选择地址由开关决定,0:按下,1:未按下

Ci, //输入选择地址由开关决定,0:按下,1:未按下

S, //输出,0:点亮,1:熄灭

Co //输出,0:点亮,1:熄灭

);

input A;

input B;

input Ci;

output S;

output Co;

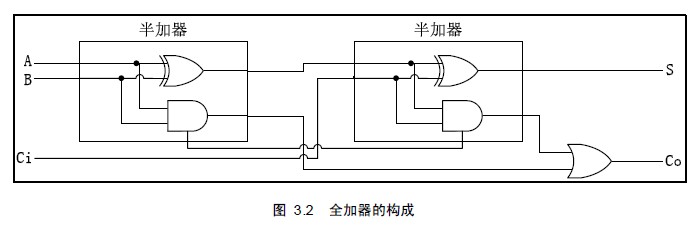

wire C0, C1;

assign Co = C0 | C1;

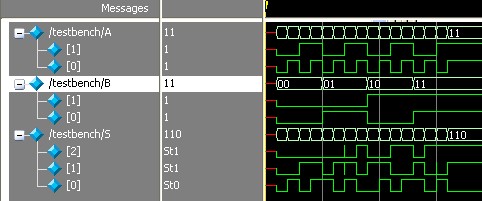

half_adder half_adder_0(.A(A), .B(B), .S(A0), .C(C0));

half_adder half_adder_1(.A(A0), .B(Ci), .S(S), .C(C1));

endmodule

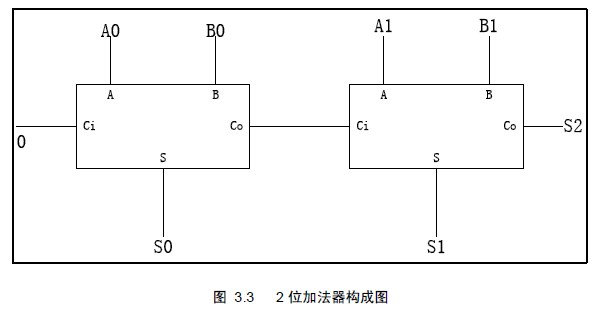

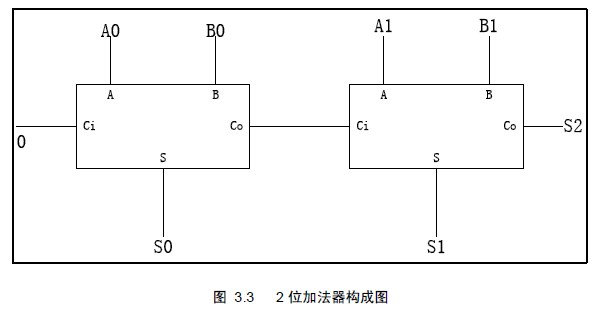

// adder.v

module adder(

A, //输入选择地址由开关决定,0:按下,1:未按下

B, //输入选择地址由开关决定,0:按下,1:未按下

S //输出,0:点亮,1:熄灭

);

input [1:0] A;

input [1:0] B;

output [2:0] S;

full_adder U1(.A(A[0]),

.B(B[0]),

.Ci(0),

.Co(C0),

.S(S[0])

);

full_adder U2(.A(A[1]),

.B(B[1]),

.Ci(C0),

.S(S[1]),

.Co(S[2])

);

endmodule

/4

/4

文章评论(0条评论)

登录后参与讨论