// fsm.v

module fsm(Clock, Reset, A, K2, K1);

input Clock, Reset, A;

output K2, K1;

reg K2, K1;

reg [1:0] state, nextState;

parameter

Idle = 2'b00,

Start = 2'b01,

Stop = 2'b10,

Clear = 2'b11;

//---每一个时钟沿产生一次可能的状态变化-----

always @(posedge Clock)

if (!Reset)

state <= Idle;

else

state <= nextState;

//-----产生下一状态的组合逻辑-------

always @(state or A)

case (state)

Idle:

if (A)

nextState = Start;

else

nextState = Idle;

Start:

if (!A)

nextState = Stop;

else

nextState = Start;

Stop:

if (A)

nextState = Clear;

else

nextState = Stop;

Clear:

if (!A)

nextState = Idle;

else

nextState = Clear;

default:

nextState = 2'bxx;

endcase

//----产生输出K1的组合逻辑--------

always @(state or Reset or A)

if (!Reset) K1 = 0;

else

if (state == Clear && !A) //...

K1 = 1;

else

K1 = 0;

//----产生输出K2的组合逻辑--------

always @(state or Reset or A)

if (!Reset) K2 = 0;

else

if (state == Stop && A) //...

K2 = 1;

else

K2 = 0;

endmodule

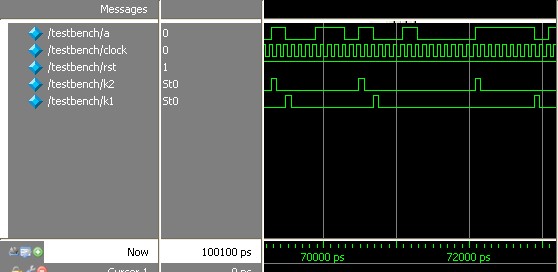

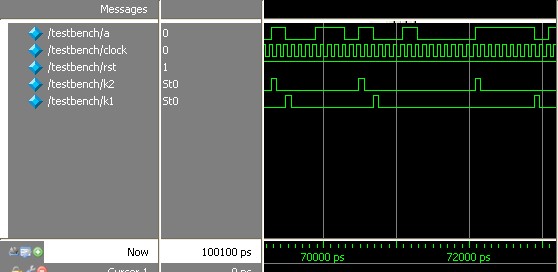

// testbench.v

module testbench;

reg a;

reg clock, rst;

wire k2, k1;

initial

begin

a = 0;

rst = 1;

clock = 0;

#22 rst = 0;

#133 rst = 1;

end

always #50 clock = ~clock;

always @(posedge clock)

begin

#30 a = ($random)%2;

#(3*50+12);

end

initial

begin

#100000 $stop;

end

//------调用被测试模块------

fsm fsm_0(.Clock(clock), .Reset(rst), .A(a), .K2(k2), .K1(k1));

endmodule

/4

/4

文章评论(0条评论)

登录后参与讨论