// tryfunct.v

module tryfunct(clk, n, result, reset);

output [31:0] result;

input [3:0] n;

input reset, clk;

reg [31:0] result;

always @(posedge clk)

begin

if (!reset)

result <= 0;

else

begin

result <= n*factorial(n)/((n*2)+1);

end

end

function [31:0] factorial;

input [3:0] operand;

reg [3:0] index;

begin

factorial = operand? 1: 0;

for (index = 2; index <= operand; index = index + 1)

factorial = index * factorial;

end

endfunction

endmodule

// tryfunct_test.v

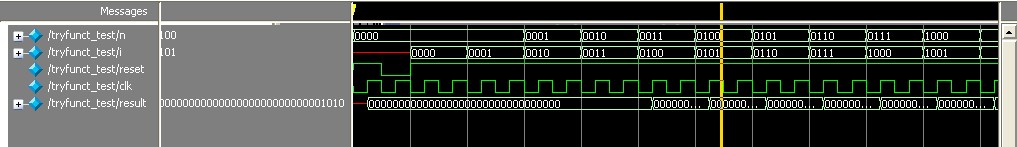

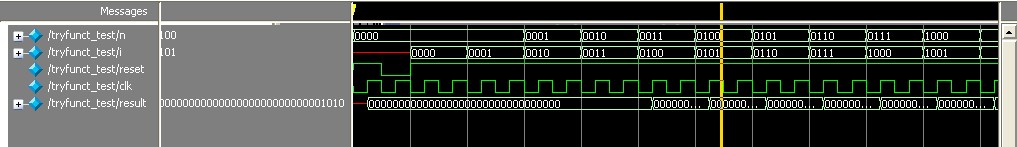

`timescale 1ns/100ps

`define clk_cycle 50

module tryfunct_test;

reg [3:0] n, i;

reg reset, clk;

wire[31:0] result;

initial

begin

clk = 0;

n = 0;

reset = 1;

#100 reset = 0;

#100 reset = 1;

for (i=0; i <= 15; i = i+1)

begin

#200 n = i;

end

#100 $stop;

end

always #`clk_cycle clk = ~clk;

tryfunct tryfunct_0(.clk(clk), .n(n), .result(result), .reset(reset));

endmodule

/4

/4

文章评论(0条评论)

登录后参与讨论