摘要:基于Cyclone II Device Hankbook的几种配置方式描述

cycloneII器件使用SRAM单元存储配置信息,由于SRAM存储器是易失性的,所以每次上电后配置信息都会重新加载到cycloneII芯片中。可以使用AS(action serial)配置方式,这需要DCLK的频率达到40MHz的情况下,配置cycloneII芯片。也可使用PS(passive serial)和JTAG(Joint Test Action Group)方式来配置。此外,cycloneII芯片还能接收压缩的配置信息比特流,在运行过程中解压这些数据,来降低存储要求和配置时间。

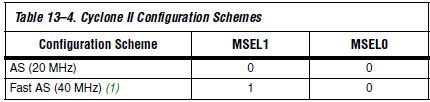

可以通过cycloneII芯片的MSEL引脚的高低来选择哪中配置方式,MSEL引脚是有其所在bank的VCCIO引脚驱动的,MSEL[1..0]引脚有9K欧的内部下拉电阻始终有效。在上电复位和重新配置时,MSEL引脚肯定是出于LVTTL Vil或者Vih电平,分别被看作逻辑低和逻辑高。因此,为了避免因使用了错误的配置方法而产生问题,需要将MSEL[ ]引脚连接到其所在的I/O bank的VCCIO和GND,不需要连上拉或下拉电阻。MESL[ ]引脚不需要处理器或其他的器件来驱动。

说明:

1.只有EPCS16和EPCS64器件需要DCLK达到40MHz的时钟,其余的EPCS只需要DCLK达到20MHz。具体的选型可参考Serial Configuration Devices Data Sheet。

2.JTAG配置的优先权高于其他的配置方式,这就意味着MSEL引脚的设置可忽略。

3.不可让MSEL引脚悬空,将他们连到VCCIO或GND,这些引脚在做成产品后支持非JTAG配置方式。如果只使用JTAG配置,可将MSEL引脚都连到GND。

下表所示的是未压缩的cycloneII配置文件的大小,在计算多种器件的配置所需的存储空间总数时,要将每个器件的文件大小相加。

上表中的数据只是估计了设计编译之前的文件大小,不同的配置文件格式,如Hexadecimal(十六进制.hex)或者Tabular Text File(表格式文件.ttf)格式,都是大小不同的。不管怎样,对于任何具体版本的QuartusII软件,对于相同器件的任何设计平台,都有的未压缩配置文件大小。如果使用压缩,那么文件的大小是可变的,因为每次编译的压缩率依赖于设计。

cycloneII器件支持在存储空间中存放压缩的配置信息。这一特性就允许在配置芯片或其他存储器中存放压缩的配置信息,并把压缩的配置信息装载入cycloneII芯片。在配置过程中,cycloneII芯片实时的解压这些bit流,并配置他的SRAM单元。

初步的数据表明,压缩可将配置bit流的大小减少35%到50%。

cycloneII芯片的AS和PS配置方式都支持解压,而JTAG模式不支持。

虽然都是使用相同的压缩运算,但是cycloneII芯片的解压特性不同于扩展配置芯片(EPC16,EPC8和EPC4)的解压特性。扩展芯片中允许存放压缩的数据,在传送到目标芯片之前进行解压。

在PS模式,要用cycloneII解压特性,因为发送压缩的配置信息可以减少配置时间。不可以同时使用cycloneII芯片和扩展配置芯片的解压特性。压缩算法不能递归,并可能增大配置文件,而不会进一步压缩。

使用AS配置模式,如果想要节省串行配置芯片的存储空间,就需要使用cycloneII芯片的解压特点。

如果使用压缩,QuartusII软件会生成一个带压缩配置信息的文件,这个压缩文件减少了配置芯片或者Flash的存储空间,也减少了将其传送到cycloneII芯片中所需的时间,cycloneII芯片解压配置文件的时间要小于传送配置信息到FPGA的时间。

有两种方法压缩cycloneII的bit流,在编译前(在Compiler Settings菜单中),编译后选择(在Convert Programming Files窗口)。

在project的编译器设置中选择是否压缩,选择Assignment菜单下的Device选项,打开setting窗口,选好所需的cycloneII芯片后打开Device&Pin Options窗口,在General 设置一栏下选中Generate compressed bitstreams。如下图所示:

也可在创建项目文件是的Convert Programming Files窗口中选择是否压缩。

1.点击File菜单下的Convert Programming Files

2.选择Programming File type。只有Programmer Object Files(.pof),SRAM HEXOUT,RBF,或者TTF文件支持压缩。

3.对于POF,要选择一个配置芯片。

4.选择Add Files和添加cycloneII SRAM Objece Files(.sof)

5.选择要添加到SOF区域的文件的名称,点击Properties。

6.选中Compression的复选框。

当有多个cycloneII 芯片级连的时候,每个芯片的压缩特性都是可选的。如下图所示:

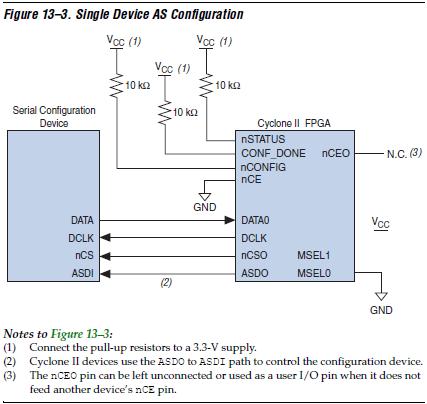

在AS配置方式下,cycloneII芯片通过一个串行配置芯片来配置。这个配置芯片是一种非易失性,有4接口的低成本芯片,这就使得串行配置芯片是一款理想的低成本的配置解决办法。

更多串行配置芯片的信息可以查看Configuration Handbook中的Serial Configuration Device Sheet部分。

串行配置芯片提供了串行接口来收发配置信息。在芯片配置期间,cycloneII芯片通过串行接口读取配置信息,如果必要的话还要解压数据,配置其的SRAM单元。

AS配置方式中FPGA控制配置接口,而PS配置方式由外部宿主(如配置芯片或者处理器)控制接口。

若使用AS模式配置FPGA芯片则cycloneII的解压特性是可以设置的,如下图所示:

单芯片AS配置:

串行配置芯片有4个接口:串行时钟输入(DCLK),串行数据输出(DATA),AS数据输入(ASDI),和一个低电平有效的片选(nCS)。这4个引脚与cycloneII芯片引脚之间的连接如下图所示:

在加电的时候cycloneII芯片通过一个POR(上电复位),在POR期间,芯片复位,保持nSTATUS和CONF_DONE为低电平,所有的可用I/O引脚为三态。通常在持续100ms的POR后,cycloneII通过10K欧姆的上拉电阻将nSTATUS引脚变为高电平,cycloneII芯片进入配置模式,一旦FPGA成功退出POR,所有的可用I/O引脚仍然保持三态。cycloneII芯片可用I/O引脚的上拉电阻在配置前和配置过程中始终是接通的。该上拉电阻的值可以通过手册的DC Characteristics &Timing Specifications查阅。

配置周期包括复位,配置和初始化阶段。详细信息可参看cycloneII数据手册的363页。

多芯片AS配置:

可以使用一个串行芯片来配置多个cycloneII芯片。可以使用片选(nCE)和片输出使能(nCEO)引脚级联多个cycloneII芯片。将第一个芯片的nCE引脚接地,将它的nCEO引脚连到下一芯片的nCE引脚。使用外部的10K欧姆的上拉电阻将nCEO信号接到VCCIO电平,协助内部微弱的上拉电阻。当第一个芯片从bit流捕获到配置数据,将其转移到nCEO引脚,开始配置下一个芯片。最后一个芯片的nCEO引脚可以不连,如果最后一个芯片是cycloneII芯片配置结束后也可以将nCEO引脚用作普通I/O。

QuartusII软件默认将cycloneII芯片的nCEO引脚作为输出引脚接到地。如果芯片是级联的,nCEO引脚连到下一个芯片的nCE引脚,在配置后需确认该nCEO引脚没有被用作普通的I/O引脚。在QuartusII软件中通过Dual-Purpose Pins中的Device&Pin Options对话框。

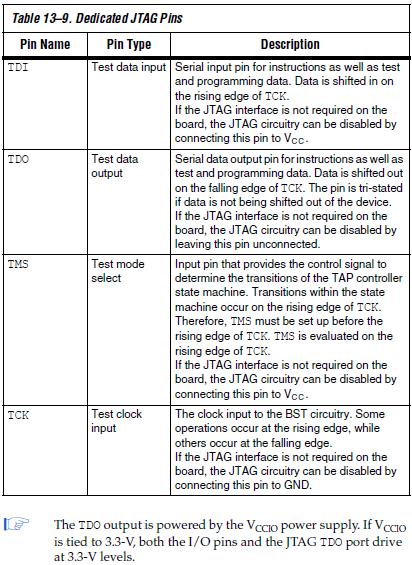

JTAG配置:

Joint Test Action Group(JTAG)已经发展成为一个边沿扫描测试的规范。边沿扫描测试(BST)的结构允许测试PCB上间距很小的器件,BST可以测试器件的引脚而不需要使用物质的探针在芯片运行时来捕捉有用的信号。JTAG电路常常被用于将配置信息转移到芯片中。QuartusII软件自动产生SOF文件,供JTAG配置,利用下载线下载到QuartusII编程器。

cycloneII芯片的设计使得JTAG的使用优先于其他的芯片配置方式。这意味著JTAG可以配置,而无需等待其他配置模式来完成。例如,在PS配置期间,想要用JTAG方式来配置cycloneII芯片,PS配置结束则JTAG配置开始。如果cycloneII芯片的MSEL引脚设置为AS或快速AS模式,在使用JTAG代替时cycloneII芯片不会输出DCLK信号。

芯片在JTAG模式下运行要使用TDI,TDO,TMS,和TCK引脚。TCK引脚内部有一个小的下拉电阻,而其他JTAG输入引脚,TDI,TMS内部有上拉电阻。在JTAG配置方式中所有可用的I/O引脚被置为三态。下图说明各JTAG引脚的功能。

未完.....

其他详细信息参看cycloneII Handbook

总结:配置数据有三种方式下载到目标器件:

FPGA主动(Active)方式;

只能够与Altera公司的主动串行配置芯片(EPCS系列)配合使用,因此此配置方式又称为主动串行AS模式。部分器件不支持此模式。

FPGA被动(Passive)方式;

由系统中的其他设备发起并控制配置过程。这些设备可以是Altera的配置芯片(EPC系列),或者是单板上的微处理器,CPLD等智能设备。FPGA在配置过程中完全处于被动地位,只是输出一些状态信号来配合配置过程。

被动方式又可细分为多种模式,包括 被动串行PS(Passive Serial)、快速被动并行FPP(Fast Passive Parallel)、被动并行同步PPS(Passive Parallel Synchronous)、被动并行异步PPA(Passive Parallel Asynchronous),以及被动串行异步PSA(Passive Serial Asynchronous)。

JTAG方式;

IEEE1149.1边界扫描测试的标准接口。大多数Altera FPGA都支持JTAG口进行配置,并支持JAM STAPL标准。从JTAG接口进行配置可以使用Altera的下载电缆,通过QuartusII工具下载也可以采用智能主机(Intelligent Host),如微处理器来模拟JTAG时序进行配置。

/5

/5

用户200186 2009-4-15 00:58

用户200186 2009-4-15 00:58

tengjingshu_112148725 2009-4-13 20:42

ilove314_323192455 2009-4-11 22:30