摘要:关于RAM的结构与性能

随机存取存储器(Random Access Memory,简称RAM):可在任何时刻随机地对任意一个单元直接存取信息。根据所采用的存储器单元工作原理的不同,又将随机存储器分为SRAM和动态存储器DRAM。DRAM存储单元结构非常简单,他所能达到的集成度远高于SRAM。

一、RAM结构

RAM主要由存储矩阵,地址译码器和读写控制电路(I/O电路)三部分组成。如下图所示:

1.存储矩阵

上图中右边灰色框内的每个小方块都代表一个存储单元,可以存储1位的2值代码,存储单元可以是静态的(触发器),也可以是动态的(动态MOS存储单元),因此有静态RAM(SRAM),和动态RAM(DRAM)之分。这些存储单元一般都按阵列的形式排列,形成存储矩阵。上图中的是64行×64列的存储矩阵,存储矩阵内共有4096个存储单元,可以认为他能存4096个字,每字的字长为1位,存储容量为4096×1位,即4K×1位。

2.地址译码器

要对上述4096个存储单元进行编码,确定地址。11位二进制数恰好可以编出2的11次方,4096个地址码,即A0A1A2A3A4A5A6A7A8A9A10A11=00000000000~11111111111。地址码A11~A0经X地址译码器(行地址译码器)和Y地址译码器(列地址译码器)译码后,就可使相应的行线(X)和列线(Y)为高电平,从而选中该地址的存储单元。很显然,只有行、列均被选中的某个单元存储电路,在其X向选通门与Y向选通门同时被打开时,才能进行读出信息和写入信息的操作。 例如,A11~A0=000000111111,经X地址译码器译码,行线X63为高电平,控制第63行的63个存储单元都与各自的位线相通,同时经过Y地址译码器译码,使列线Y0为高电平,使第一列的位线控制门(T0,T0')导通。总之经行,列译码,使相应的存储单元(63,0)与D,![]() 端接通,所以只对该单元进行读写。

端接通,所以只对该单元进行读写。

实际RAM都为大规模集成片,其存储容量都比图中的大,若地址码位数(即地址线条数)为n,则可寻址位数为2的n次方位。图中所示的存储体是容量为4K×1位的存储器,因此,它仅有一个I/O电路。如果要组成字长为4位或8位的存储器,则每次存取时,同时应有4个或8个单元存储电路与外界交换信息,这种存储器中,将列按4位或8位分组,每根列选择线控制一组的列向门同时打开;相应地,I/O电路也应有4个或8个。每一组的同一位,共用一个I/O电路。通常,一个RAM芯片的存储容量是有限的,需要用若干片才能构成一个实用的存储器。这样,地址不同的存储单元,可能处于不同的芯片中,因此,在选择地址时,应先选择其所属的芯片。对于每块芯片,都有一个片选控制端(![]() ),只有当片选端加上有效信号时,才能对该芯片进行读或写操作。一般,片选信号由地址码的高位译码产生。

),只有当片选端加上有效信号时,才能对该芯片进行读或写操作。一般,片选信号由地址码的高位译码产生。

3.片选与读/写控制电路(I/O电路)

数字系统中的RAM一般有多片组成,而系统每次读写时,只针对其中的一片(或几片)。为此在每片RAM上加有片选端![]() 。

。

当![]() =1时,三态门G1、G2、G3均为高阻态,不能对该片读写,故未选择此片。

=1时,三态门G1、G2、G3均为高阻态,不能对该片读写,故未选择此片。

当![]() =0时,选中此片。若读/写控制端R/

=0时,选中此片。若读/写控制端R/ ![]() =1,则G2工作,G1,G2呈高阻态阻断。若按上述给出地址码A0A1A2A3A4A5A6A7A8A9A10A11=00000000000~11111111111,则(63,0)单元的数据即可经位线、T0、G2读出到I/O端,完成读操作;若R/

=1,则G2工作,G1,G2呈高阻态阻断。若按上述给出地址码A0A1A2A3A4A5A6A7A8A9A10A11=00000000000~11111111111,则(63,0)单元的数据即可经位线、T0、G2读出到I/O端,完成读操作;若R/ ![]() =0,则G1、G3工作,G2阻断,I/O端的数据经G1、G3、T0、T0'、位线写入(63,0)单元,完成写操作。

=0,则G1、G3工作,G2阻断,I/O端的数据经G1、G3、T0、T0'、位线写入(63,0)单元,完成写操作。

上图中为静态RAM×1结构的原理图,其电气特征是:只有一个DB及其电路。图中地址线与芯片内单元容量一一对应,R/ ![]() 为读写控制,

为读写控制,![]() 为片选控制。

为片选控制。

下图为静态RAM×2结构的原理图,一条Y地址译码线控制相邻两列列选门控,它有两个DB及其电路。其余同×1结构。×4、×8结构可类推。

二、RAM存储单元

1.MOS静态存储单元

(利用触发器的记忆功能,存储数字信息)

静态存储器的基本存储单元电路如图上所示,它是在MOS型双稳态触发器的基础上增添了两个门控管,即六管CMOS静态存储单元。图中T1、T2和T3、T4两个反相交叉反馈,构成基本的R-S双稳态触发器,两个稳定状态分别表示1或者0,例如A点为高电平,B点为低电平,表示存1,相反则表示存0。T5、T6是由行线X控制的门控管,控制触发器与位线的通断。当行选择线X为高电平时,T5、T6管导通,A点和B点分别与内部数据线D和![]() (也称位线)接通。T7、T8也是门控管,控制该存储单元的内部数据线是否与外部数据线接通。当列选择线Y也为高电平时,T7、T8管通,内部数据线与外部数据线接通,表示该单元的数据可以读出,或者把外部数据线上的数据写入到该存储单元。

(也称位线)接通。T7、T8也是门控管,控制该存储单元的内部数据线是否与外部数据线接通。当列选择线Y也为高电平时,T7、T8管通,内部数据线与外部数据线接通,表示该单元的数据可以读出,或者把外部数据线上的数据写入到该存储单元。

2.MOS动态存储单元

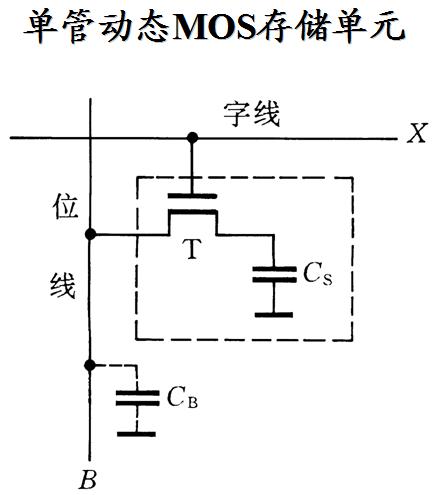

(1)单管NMOS动态存储单元

单管NMOS动态存储单元如下图,它由一个门控管T和一个存储信息的电容CS组成。

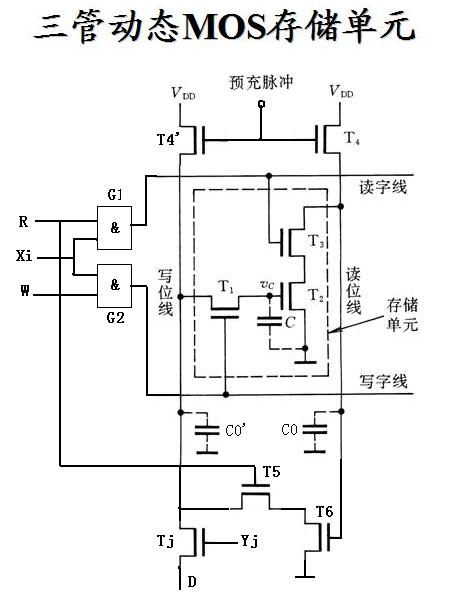

(2)三管NMOS动态存储单元

桑NMOS动态存储单元如下图中虚线框内所示,它只用NMOS管T2的栅电容C来暂存数据。

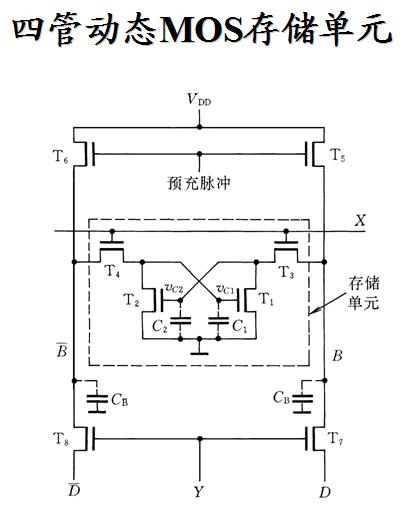

(3)四管NMOS动态存储单元

三、RAM扩展

RAM扩大存储容量的方法,通常有位扩展和字扩展两种。如下图所示:

四、SRAM与DRAM比较

动态存储单元的结构比静态存储单元简单,可以达到更高的集成度。但DRAM需要不断循环刷新,不如SRAM使用方便,而且存取时间也较长。

未完.......

tengjingshu_112148725 2009-4-17 09:12

用户200186 2009-4-15 20:03

用户1410360 2009-4-15 19:47

用户200186 2009-4-15 01:01

tengjingshu_112148725 2009-4-13 20:43