双向口通路问题之最终释疑

前一篇短文问好像没有把问题描述清楚,现在把仿真结果、关键代码贴出来一起回顾这个问题,并尝试着给出解释。<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

双向口电路基本格式:

ENTITY bidir_pin IS

Port (

bidir : INOUT std_logic_vector(3 downto 0);

from_core : IN std_logic_vector(3 downto 0);

oe :IN std_logic;

to_core : OUT std_logic_vector (3 downto 0)

) ;

END bidir_pin;

ARCHITECTURE behavior OF bidir_pin IS

BEGIN

bidir <= from_core WHEN oe=’1’ ELSE “ZZZZ”; --输出口。 oe为’0’时三态门为高阻,此时bidir为输入端口。这里的情形刚好与论文《FPGA中双向端口I/O的研究》相反。

to_core <= bidir; --输入。 注意这里并没有用oe条件去刻画输入端口,有一种默认的意味在里面。

END behavior;

在Quartus平台下解析后(Elaboration)的RTL级视图如下:

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

图1 RTL级视图

在Quartus平台下编译该文件并进行功能仿真可得到下面的仿真波形图:

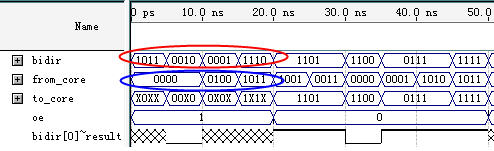

图2 双向口功能仿真图形

从图中可见,当oe不等于’1’ 时,to_core <= bidir是成立的,也就是说此时bidir作为输入端口。对于oe为’1’ 时的情形,如果按照事先设想,bidir应为输出端口,将执行bidir <= from_core操作,也就是上图中红色圈中的”uuuu”应被下方蓝色圈中的数据取代。

从结果可见上面的设想并没有实现。bidir仍旧保持为”uuuu”,换句话说bidir此时并没有成为输出端口。

还有一个疑点,当oe=’1’时,用to_core上却在bidir的端口上(此时bidir作输出口)读到高阻态。按道理说,此时to_core没有被使用(应为此时bidir作为输出口而不是输入口),但仿真中却读到高阻态,而且和不知何故产生的bidir~result相同,真是让人莫名其妙!

织女星猜测产生这个现象的原因要么是Quartus不能对双向口inout进行输出仿真,也就是无法在bidir作为输出口时观察bidir线上输出的from_core数据;要么就是需要在代码中添加寄存器来读出bidir线上的输出数据。

希望尽快找到这个问题的真相......

经过织女星同志一天的思考,发现原因其实很simple!

原来是我把from_core、to_core分别定义成输入、输出端口了!Quartus会严格按照我对端口性质的定义去工作。换言之,就是被定义成输出端口的(如本文中的to_core),就只能做输出观察使用;而被我定义成输入端口的from_core就只能做输入端口使用!

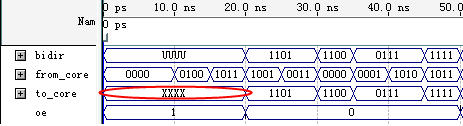

各位请仔细看图2,比较一下红蓝两圈中的数据,是不是发现了什么相似之处?当oe=’1’时,三态门开启,from_core的数据和bidir上的数据(已被我在仿真图中赋予了初值——见图2红色圈中数据)一起涌向了to_core,造成数据冲突,这样就使得红、蓝两圈中数据对应位不一致时,输出为 ’x’ 的现象!例如当bidir为”1011”,from_core为”0000”时,to_core为”x0xx”。可以猜想,当bidir为”uuuu”时,to_core就应该是”xxxx” !呵呵,下面的仿真图佐证了这一点。

图3

至于bidir~result,只是Quartus自动生成的测试端口而已。

终于真相大白了。回顾整个过程,发觉敏锐的眼光、审慎的思考及严谨的态度对于一名优秀的电气工程师而言实在是太重要了!希望拙文能对疑惑于inout仿真的朋友有所裨益。

/2

/2

文章评论(0条评论)

登录后参与讨论