阻塞与非阻塞( block & non-block)

两种赋值方法,区别如下:

Block: “=”,阻塞即阻塞后面的赋值语句进行,直到该句计算完RHS,并赋给LHS.计算RHS期间不允许其它语句执行.在always里可以看作是顺序执行的.

Non-block: “<=”,非阻塞即允许其它赋值语句同时进行,且进入always里前,RHS已计算好,进入后更新LHS,所以always里的语句可以看作并行的.

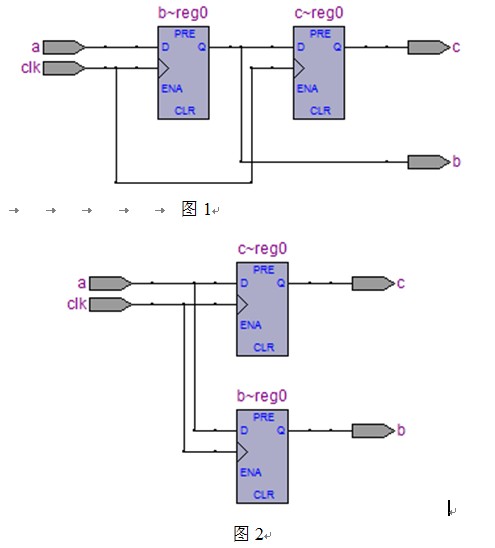

一个简单程序说明:

module regout(a,b,c,clk);

output c,b;

input clk,a;

reg b,c;

always @( posedge clk)

begin

b<=a; //=为图2

c<=b; //=为图2

end

endmodule

基于上述特点,在进行赋值时,应遵循以下原则:

1>.时序电路,用非阻塞赋值.

2>.锁存器电路,用非阻塞赋值.

3>.用always里建立组合逻辑时,用阻塞赋值.

4>.在同一个always里建立时序和组合逻辑时,用非阻塞.

5>.在同一个always里不要同时有阻塞和非阻塞.

6>.不要在一个以上的always块里为同一个变量赋值.

7>.用$strobe显示用非阻塞赋值的变量值.(not clear)

8>.在赋值时不要使用#0延迟.(not clear)

整理于夏宇闻的书,

书中还有实例

/4

/4

文章评论(0条评论)

登录后参与讨论