(三)FIR滤波器的FPGA设计

y(n) = h(0)x(n) + h(1)x(n-1) + h(2)x(n-2) + …… + h(N-1)x(n-N+1)

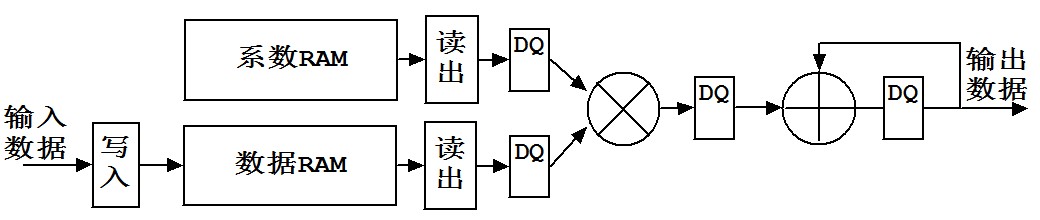

可知,FIR滤波过程是一个串行相乘累加的过程。一次FIR时域卷积运算需要242次乘加。如果采用直接型结构,则在一次数据输入时间内,需要进行242次运算。最小资源要求,242*16bit的ROM大小,242*8bit的RAM大小,最少有一个16*16bit的乘法器。直接型结构图如下:

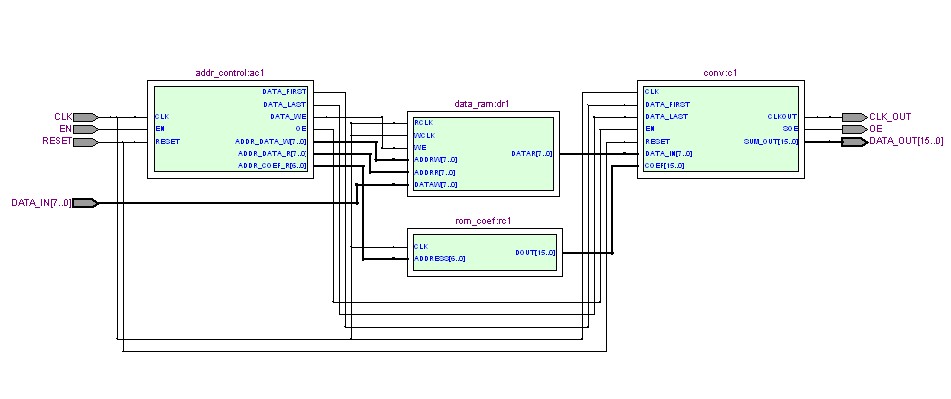

电路主要由四个模块构成:

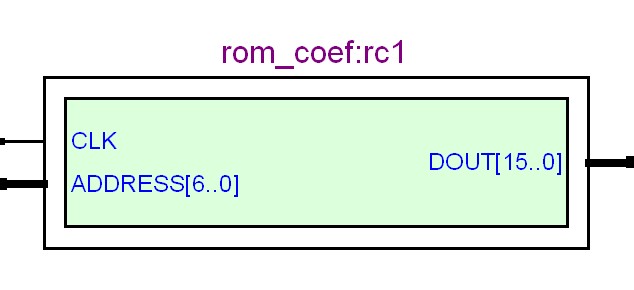

系数ROM表:

用于保存242个抽头系数。深度为7bit,位宽16bit。

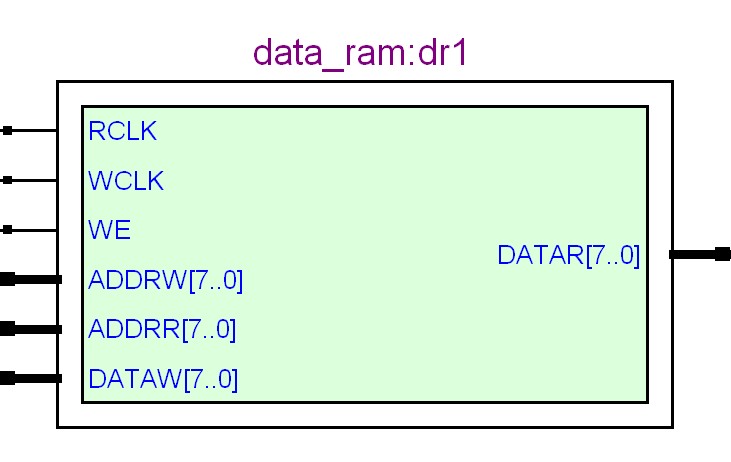

数据双口RAM:

用于缓存输入数据,深度一样为8bit,位宽也为8bit。

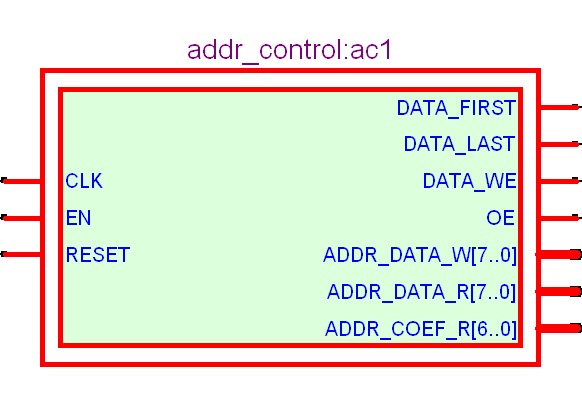

地址控制模块:

用于产生系数ROM的读地址和数据RAM的读写地址,以及后级串行卷积电路的控制信号,从而控制数据的缓存和读写。

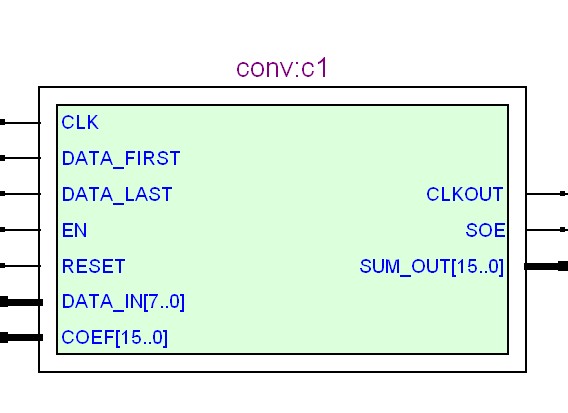

串行卷积模块:

核心的运算模块,采用流水线进行相乘累加。其中,在对相乘累加后的数据进行了截取,截取方式:

相乘累加结果:sum[23:0] signed;

卷积输出结果:SUM_OUT[15:0] signed;

SUM _OUT = sum[22:7];

由于是有符号数相乘,最高两位都是符号位,所以舍弃最高位的符号位,另外再截取低7位的数据。 /5

/5

文章评论(0条评论)

登录后参与讨论