悲剧啊……跳闸啦,刚码到一半……又要重新码啊……![]()

我们先来搞清楚两个概念——“逻辑分区”和“物理分区”。

前面所讲到的Design Partition只是将设计进行“逻辑分区”,直白点说就是将我们的设计分成N个小的模块,每个模块有着单独的逻辑和功能,它告诉编译器,这部分逻辑是一个分区A,那部分逻辑是另一个分区B,在进行这样的分区之后,编译器在整个工程的综合、布局布线上面并不会有什么太大的变化,这个逻辑上的分区只是用来让用户清楚,哪部分逻辑是分区A的,哪部分逻辑是分区B的。之后用户就可通过设定A、B分区的属性类型来告诉编译器,哪部分已经不需要重新综合、布局布线了;哪部分已经修改了,需要重新进行综合等等。

而我们来看看LogicLock的作用,是对设计进行“物理分区”,更准确的说,它是对目标器件进行“物理分区”,然后将逻辑上的功能模块分配到一定的分区内。也就是说,我们先对目标器件进行物理区域划分,把它分成几个“地盘”,然后选择一个逻辑功能模块分配到某个“地盘”里,告诉编译器,以后这部分逻辑功能就只能在这个“地盘”里面布局布线了。同样的,用户可以对各个模块进行属性上的设定,告诉编译器以什么样的形式在“地盘”里面进行布局布线。

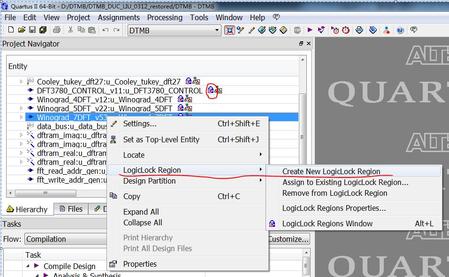

下面简单介绍下LogicLock的使用,我们前面已经用Design Partition进行了“逻辑分区”,我们可以用同样的方法,在设计的树形结构里面右键,然后如下图:

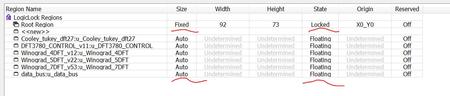

把各个子模块加入到LogicLock Region里面之后如下图:

里面有两个主要的参数,Size和State:Size有两个选项,Auto、Fixed;而State也有两个选项,Locked、Floating。但是并不是有着四个组合,其实只有着下面三种状态:

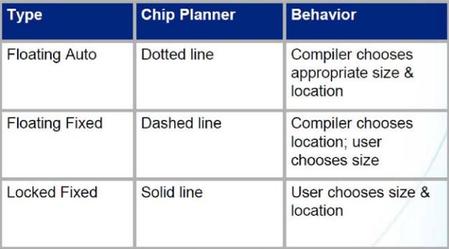

第一种,Auto+Floating:由编译器自动选择区域大小和位置;(在Chip Planner里面由虚线显示)

第二种,Fixed+Floating:由编译器选择位置,但由用户设定区域大小;(在Chip Planner里面由短实线显示)

第三种,Fixed+Locked:区域大小和位置都由用户来设定。(在Chip Planner里面由实线显示)

那我们来说说LogicLock在增量编译里面有什么作用呢?还是需要强调一下,增量编译不是一定非要用到LogicLock,但Quartus推荐在增量编译时使用LogicLock!为什么呢?因为它可以让增量编译的思想贯彻得更彻底。

我们想想在前面用Design Partition时出现的一种情况:改动后的模块逻辑功能上变化比较大,影响了其它“逻辑分区”的布局布线,这样未改动部分也需要进行重新编译了。但如果这个时候使用的是LogicLock,由于每个逻辑功能模块都分配了一定的“物理区域”,改动后的模块再怎么变也是在它自己的“地盘”里,不会影响到别的“地盘”的布局布线。

但LogicLock也会带来一定的负面影响,最直接的,一般情况下,时序分析后的Fmax都要更低一些。这是为什么呢?其实想想也能知道,如果没有使用LogicLock,编译器可以自动从全局出发去做出做大的优化,而我们人为地进行了物理分区限定,那即使可能每个小模块做到了很好的优化,但是由于各个区域之间的布局布线受到了限制,那自然会有所影响。但也不能如此绝对地断定,如果在占用资源很庞大的情况下,使用这种方法还能带来意想不到的效果。

jlx_cuc 2013-7-24 14:00

用户443471 2013-7-23 23:15

用户443471 2013-6-29 22:12

用户377235 2013-4-26 08:18

jlx_cuc 2012-10-26 13:54

用户561495 2012-10-25 22:42

jlx_cuc 2012-10-9 09:18

用户403664 2012-10-9 09:00