硬件部分:

一:用户自定义设计好之后,将其按照Avalon总线规范进行封装,添加到系统中,如下,添加新的component,即你的世设计

添加完你的component,在tools-options下指定你的设计的路径,防止下一次打开后找不到你的设计

二:将你需要的IP添加到你的系统中,部分IP是设计好的,部分可能需要你自己进行设计,共同的特点是需要Avalon总线封装。

IP添加完之后,为每个模块分配基地址和中断,这些都是自动的,一般没有必要进行修改。

分配完之后点击generate即可产生你的Nios II系统了。。这个过程比较长,主要会产生很多硬件信息,为下面的软硬件设计做准备。

三:新建一个bdf文件,将生成的硬件电路图加入其中,添加输入输出管脚及其他模块,如锁相环等,

分配管脚,每个开发板在买的时候可能都会提供一个管脚配置文件,只需按照相应的名称命名然后自动导入即可,

最后综合,时序分析。。硬件部分完成。

软件部分:

一:新建工程,

二:指定硬件信息文件(ptf文件,在上面generate时会产生),选择工程模版

三:选择system library的一些属性,便于编译等工作

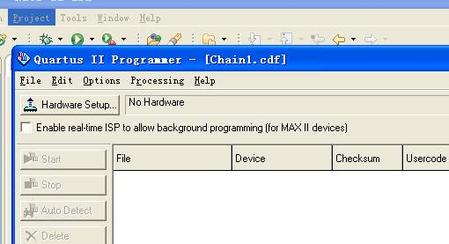

四:编写代码,调试,直到ok,下载硬件信息

四:下载软件代码,完毕

参考书籍:

这些很容易在网上找到

Avalon总线规范.pdf

NIOSII那些事儿REV7.0.pdf

NIOS最佳教程.pdf

挑战Soc--基于Nios的SOPC设计与实践.pdf

/4

/4

文章评论(0条评论)

登录后参与讨论