第二章 架构

(由于字数限制,采用一键排版,所以效果不好,还请见谅)

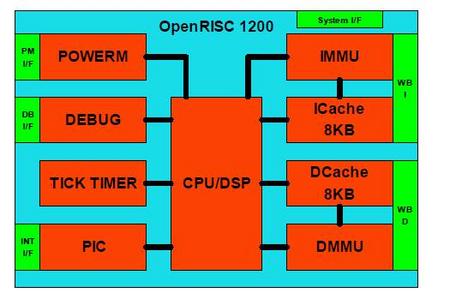

图1给出了OpenRisc 1200IP核的架构,包括如下模块:

CPC/DSP核心模块

直接映射数据cache

直接映射指令cache

基于Hash基于DTLB的数据MMU

基于Hash基于DTLB的指令MMU

功耗管理单元及功耗管理接口

定时器

用于开发和调试的接口

中断控制器及中断接口

基于Wishbone的指令和数据接口

图1

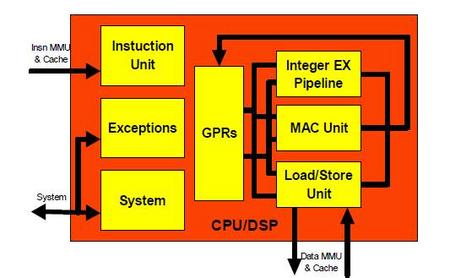

CPU/DSP

CPU/DSP是OpenRisc1200处理器的核心单元,图2给出了CPU/DSP的基本结构图。

图2

OpenRisc1200 CPU/DSP 仅仅实现了OpenRisc1000架构的32位部分,64位中的浮点运算和向量操作并未实现。

指令单元(Instruction unit)

指令单元实现了基本的指令流水线,从存储子系统中取指令,将它们送至可执行单元执行,维持历史状态确保之前的异常模块及其操作按照顺序完成,另外也执行条件分支和无条件跳转指令。

当执行单元可用时,Sequencer会在每个时钟把一系列指令送去执行,执行单元必须能够识别源数据是否可用及确保无其它指令会索取相同目标寄存器中的数据。

指令单元仅能实现ORBIS32指令集,当前的OpenRisc1200 不支持ORFPX32/64 and ORVDX64。

通用目的寄存器(GPRS)

OpenRISC 1200实现32个通用32位寄存器。OpenRISC 1000架构还支持寄存器文件的shadow copies以便在工作环境中来实现快速切换,然而这个功能在当前OR1200并未实现。 OR1200采用两个同步双端口存储器(32words*32bits)实现了通用寄存器文件。 存取单元(Load/Store Unit,LSU)存取单元在GPRs和CPU内部总线直接传输所有类型的数据,它采用单独的执行单元实现,因而,如果出现数据相关时,存储器子系统中的stalls仅仅会影响master流水线。

下面是LSU的主要特点:

所有的存取指令都采用硬件实现(也包括原子指令)

地址入口缓存(address entry buffer)

流水线操作

快速存储访问时采用对其访问方式

当存取指令发送时,LSU会确定是否所有的操作都是可执行的,包括:

地址寄存操作(address register operand)

源数据寄存操作(source data register operand for store instructions)

目的数据寄存操作(destination data register operand for load instructions)

整数执行流水线(Integer Execution Pipeline)

核采用32位整数指令实现下面的指令:

算术指令

比较指令

逻辑指令

翻转和移位指令

大部分的整数指令可以在一个周期内执行完毕,更多详细的关于时序的内容请参考表TBD。

MAC单元(MAC unit)

MAC单元执行DSP MAC指令,MAC操作是32*32 with 48-bit的累加器,MAC单元全部采用流水线,在任意一个时钟都可以接受新的MAC操作。

系统单元(system unit)

系统单元连接其它没有连接到指令和数据接口的CPU/DSP信号,它也实现了所有的系统目标寄存器(如管理员寄存器)。

异常(exception)

在异常条件发生时会产生核异常,在OR1200核中的异常来源有以下:

外部中断请求

某些存储器访问情况

内部错误,如尝试执行不能执行的指令

系统调用

内部异常,如断点异常

异常操作对于软件用户而言是透明的,其它异常也采用同样的机制。当一个异常发生时,控制信号会发送到异常处理程序中,异常在管理模式中进行处理。

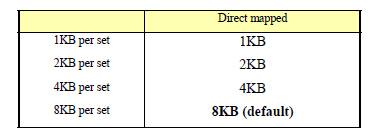

数据缓存(Data Cache)

默认的OR1200数据缓存大小配置是8-Kbyte,1-way direct-mapped,运行快速内核访问数据。另外,数据缓存可以进行如下从新配置。

特点:

数据缓存独立于指令缓存(哈弗结构)

数据缓存采用a least-recently used (LRU)替代算法实现

缓存目录采用物理寻址方式,物理地址的tag存储在缓存的目录中

支持连续写操作

靠写特殊的目的寄存器可实现无效和非使能

缓存采用16bytes突发长度进行组织,突发组织被描述为关键字先操作,关键字同时写入cache中,然后是请求单元(requesting 单元),因而由于cache fill延时的原因会使stalls最小化。Cache 为cache tags和cache line替换功能提供存储单元。

数据cache和外部接口是紧密耦合的,能够允许有效的访问系统存储控制器。

数据cache利用32bits的且连接至LSU单元的接口为GPRs单元提供数据,LSU单元同所有的逻辑用于计算有效地址,控制数据输入输出数据cache时的边界对齐,维持存取操作的秩序。数据缓存的写操作可以是整字节的,半字的或全字的。

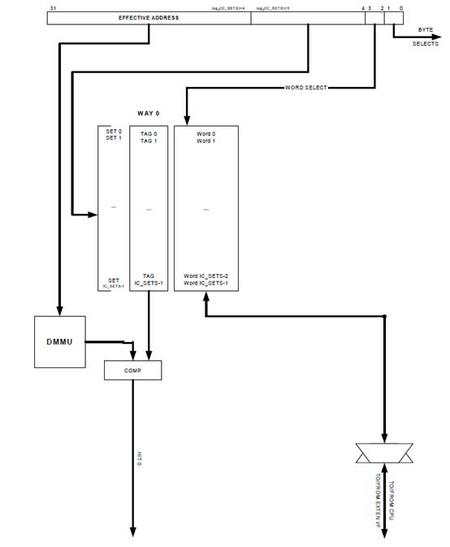

数据缓存按照512 sets of one line进行组织的,每行包括16字节,状态位及地址标记。

每行包含4个来自存储器的连续字节,这些字节在存储器中是边界对齐的。这样cache line也与页边界对齐。

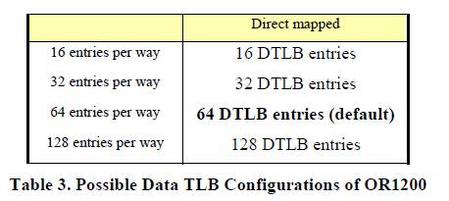

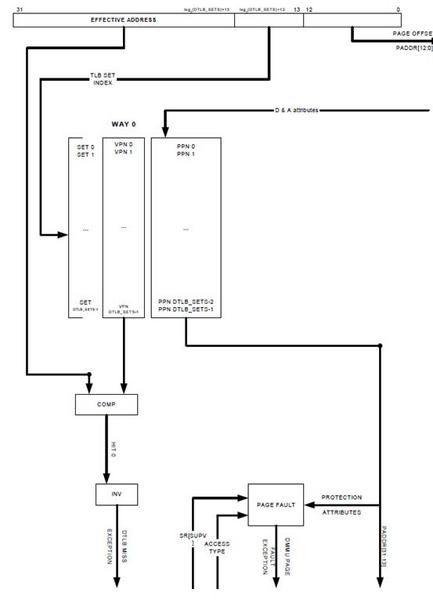

Data MMU

OR1200实现了虚拟内存管理,能够提供内存访问保护和有效的物理地址转换,保护粒度(protection granularity)被OR1000架构-8KB和-16KB所定义。

特点:

Data mmu独立于指令mmu

页大小为8KB

全面的页保护机制

默认情况下1-way direct mapped hash based translation lookaside buffer (DTLB)

Miss和fault 异常

软件 tablewalk

由于基于hash方式因而提供高性能

可变数目的DTLB,默认情况下64个

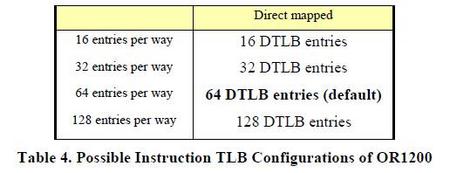

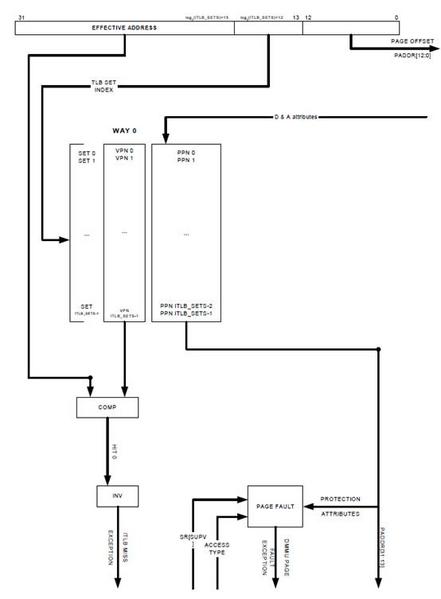

指令MMU(Instruction MMU)

OR1200实现了虚拟内存管理,能够提供内存访问保护和有效的物理地址转换,保护粒度(protection granularity)被OR1000架构-8KB和-16KB所定义。

特点:

Data mmu独立于指令mmu

页大小为8KB

全面的页保护机制

默认情况下1-way direct mapped hash based translation lookaside buffer (DTLB)

Miss和fault 异常

软件 tablewalk

由于基于hash方式因而提供高性能

可变数目的DTLB,默认情况下64个

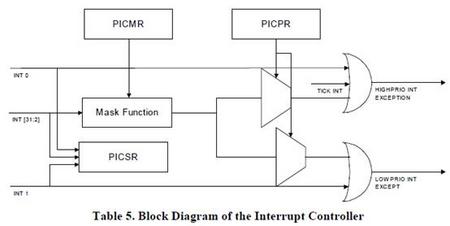

可编程中断控制器(Programmable Interrupt Controller)

中断控制器接收外部中断源并且决定它们在CPU中执行优先权。

可编程中断控制器有三个特别的目标寄存器和32个中断输入,中断输入0和中断输入1一直使能,分别连接到最高和最低优先级中断输入上。另外30个中断输入可以通过可编程目的寄存器进行屏蔽和使能。

定时器(Tick Timer )

OR1200实现了定时器功能,该定时器基于RISC时钟,可用于操作系统中精确时间的测量和时间有关的系统任务。

OR1200中定时器做如下定义:

最大可计数到2^32个时钟

中断之间的最大时间为2^28个时钟

可屏蔽的定时器中断

单一的、可重启的和继续的定时器

定时器操作来自独立的时钟源以便休眠功耗管理模式可以实现。

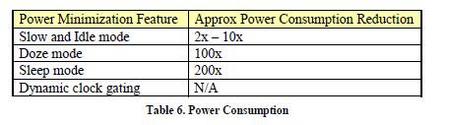

功耗管理支持(Power Management Support)

为了优化功耗消耗,OR1200提供了低功耗模式以便能够动态激活或屏蔽一些内部模块的运行。

OR1200在优化功耗消耗方面有三个特点:

低速和空闲模式(slow and idle 控制时钟的降低)

休眠模式(doze and sleep mode,中断激活)

低速模式采用外部低功耗分频的优点来实现全部的功能,在低频模式下功耗也会跟着降低。

PMR[SDF]4bits在pm_clksd信号上进行广播,外部时钟产生用适用pm_clksd信号。

当软件初始化doze模式后,软件处理被挂起。RISC内部模块的时钟信号均被屏蔽,除了定时器单元。然而另外其它片上模块仍然可以正常工作。

当推迟中断(pending interrupt)产生时OR1200从doze模式进入正常的模式。

在sleep模式,所有OR1200的内部单元被屏蔽和采用门控时钟。任意实现可以采用OR1200核低电压进行操作。

当推迟中断(pending interrupt)产生时OR1200从sleep模式进入正常的模式。

动态的门控时钟(unit clock gating on clock by clock basis)在OR1200核中并不支持。

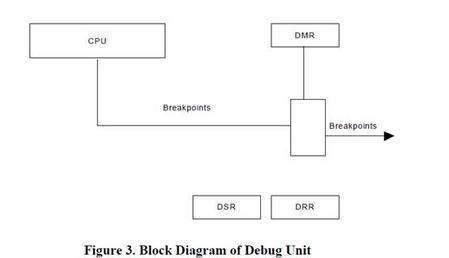

调试单元(Debug unit)

调试单元帮助软件开发者调试他们的系统,它能够提供基本的调试,但是不支持OR1000架构中的诸如watchpoint,breakpoint,program-flow control register等高级调试。

Watchpoint和breakpoint是事件触发,基于调试寄存器中可编程和或者数据流条件(by program- or data-flow matching the conditions)。Breakpoint不同于Watchpoint会暂停当前编程流的执行而开始断点异常处理。

时钟和复位(Clocks & Reset)

OR1200有一些时钟输入端,clk_cpu是cpu/dsp模块的时钟端,其它模块也有相应的时钟输入信号。Data cache的时钟信号是clk_dc,instruction cache的时钟信号是clk_ic,data mmu模块的时钟是clk_dmmu,指令mmu的时钟是clk_immu,定时器模块的时钟是clk_tt。所有的时钟要尽可能的都有相同的相位和时钟偏移。

OR1200采用异步复位信号,复位信号为rst,当检测到为高电平时,立刻复位所有的ff,当没检测到是,OR1200开始复位异常。

Wishbone 接口(Wishbone interface)

有两组wishbone接口连接到OR1200核,它们也连接到外部设备和存储器子系统中。它们符合Wishbone SOC连接规范,总线宽度是32bits,不支持其它总线宽度。

/2

/2

文章评论(0条评论)

登录后参与讨论