可以参考:

《步步惊芯--软核处理器内部设计分析》

《CPU源代码分析与芯片设计及Linux移植》

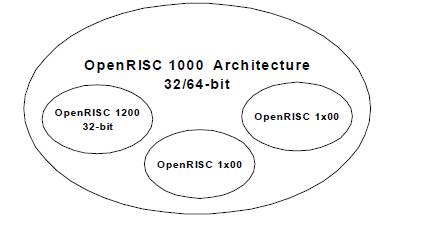

第一章 简介 本文档的目的是对OpenRISC 1200的设计进行说明。本说明书定义的已经实现具体变量并不在通用架构说明书中出现。这包括数据和指令缓存类型和大小,指令MMU(虚拟内存)的类型和大小,中断控制器、异常单元的实现及其他附属单元。 本文档不包括通用架构的主题诸如指令集,存储器寻址方式及其它架构的定义。其它详细的内容可以参考 OpenRisc 1000手册。 OpenRisc 家族OpenRisc 1000是开源RISC处理器架构家族中的一员,作为架构,它可以进行单芯片或者系统实现,可以应用于不同价格和性能需求的项目中。它采用32/64位存取RISC架构,着重点在于高性能、低功耗、可扩展性和通用性。OpenRisc 1000架构目标是中高端网络、嵌入式、自控及便携式computer市场。

所有的OpenRisc实现,第一个数字是1的都隶属于OpenRisc 1000家族,第二个数字表示OpenRisc 1000架构实现的特点及他用何种方式实现的。最后两个数字表示在实际应用之前该实现是如何进行配置的。

OpenRisc 1200

OpenRisc 1200是32位的标量采用哈弗结构的RISC,采用5级流水线,支持虚拟内存(MMU)和DSP功能。默认情况下,它是1-way direct-mapped 8KB data cache及1-way direct-mapped 8KBinstruction cache, each with 16-byte line size,且cache是物理标记的。默认情况下,MMU是被实现的,由64-entry hash based 1-way direct-mpped data TLB and 64-entry hash based 1-way direct-mapped instruction TLB.构成。其它还包括支持实时调试的调试单元、高精度的定时器、可编程中断控制器、功耗管理单元等。OR1200在使用0.18um及6层金属工艺时,主频可以运行在300MHz,可以提供300Dhrystone、2.1MIPS和300次的 32x32 DSP乘加操作,比其它同类产品高出20%的性能,默认配置下进行流片时约有100万个晶体管。

OpenRisc 1200主打嵌入式、网络及便携式设备,比起其它同类32标量处理器产品具有很强的竞争力,能够很好的运行于现在的操作系统中,竞争对手可以包括ARM10,ARC及Tensilica RISC处理器。

主要特点

下面给出了OpenRisc 1200IP核的主要特点:

用户可以自行配置IP核的一些参数

使用0.18um及6层金属工艺时,主频可以运行在300MHz,可以提供300Dhrystone、2.1MIPS

高性能的cache和MMU子系统

采用Wishbone总线结构,可以方便的进行片上系统设计

/3

/3

用户1651405 2014-3-3 17:11