三:数据和指令高速缓存(Icache,Dcache)

OR1200数据高速缓存与指令缓存的机制是一样的,仅一数据缓存为例。OR1200数据高速缓存的默认配置是8KB的一条通道直接映射的数据高速缓存,它允许CPU核心快速访问数据。数据高速缓存也可以配置为1、2、4、8KB的形式,其特征如下:

数据缓存独立于指令缓存(哈弗结构)

数据缓存采用a least-recently used (LRU)替代算法实现

缓存目录采用物理寻址方式,物理地址的tag存储在缓存的目录中

支持连续写操作

靠写特殊的目的寄存器可实现无效和非使能

缓存采用16bytes突发长度进行组织,突发组织被描述为关键字先操作,关键字同时写入cache中,然后是请求单元(requesting 单元),因而由于cache fill延时的原因会使stalls最小化。Cache 为cache tags和cache line替换功能提供存储单元。

数据cache和外部接口是紧密耦合的,能够允许有效的访问系统存储控制器。

数据cache利用32bits的且连接至LSU单元的接口为GPRs单元提供数据,LSU单元同所有的逻辑用于计算有效地址,控制数据输入输出数据cache时的边界对齐,维持存取操作的秩序。数据缓存的写操作可以是整字节的,半字的或全字的。

数据缓存按照512 sets of one line进行组织的,每行包括16字节,状态位及地址标记。每行包含4个来自存储器的连续字节,这些字节在存储器中是边界对齐的。这样cache line也与页边界对齐。

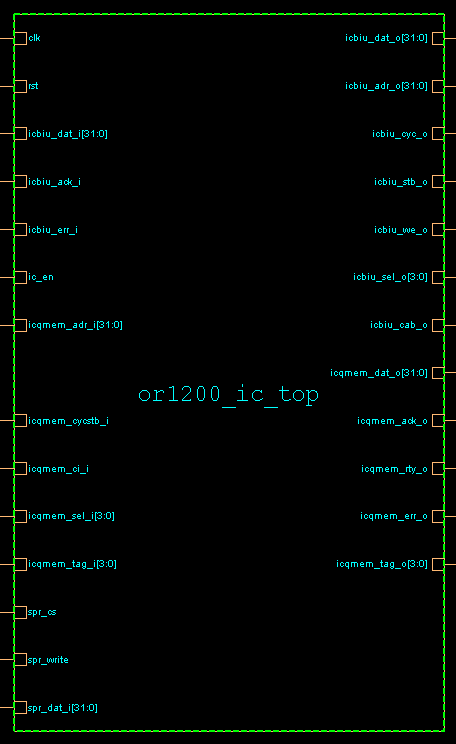

RTL级代码分析:(data cache 和 instruction cache)

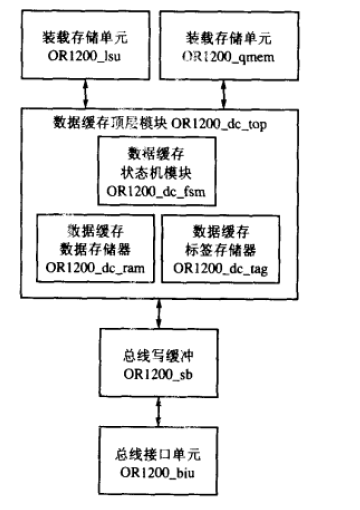

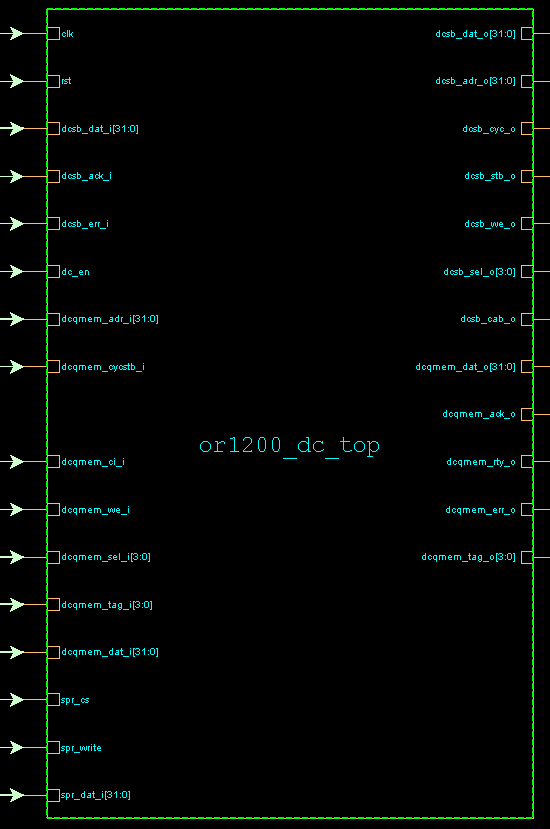

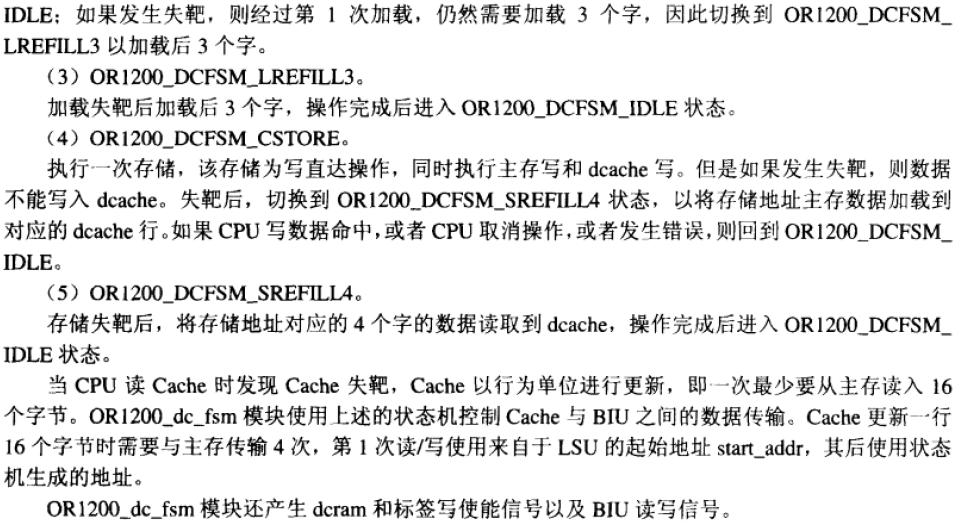

从RTL层级也可以看出data cache 和instruction cache的机制是一样的,包括缓存状态机模块(or1200_dc_fsm),缓存数据存储模块(or1200_dc_ram),缓存标签存储器(or1200_dc_tag),它们与其它模块的连接关系可以由下图示意出:

模块图:

OR1200数据缓冲存储器由两部分构成,即OR1200_dc_tag模块和OR1200_dc_ram模块。Dcache的默认大小为8KB,dcache共512行,每行由16个字节,1个标志地址标签有效的状态位和19位的地址标签组成。因此缓存行内的偏移为4,可由虚拟地址的低4位得到。OR1200_dc_ram的默认大小为2048*32位,OR1200_dc_tag的默认大小为512*20位,他们都是同步ram。Dache采用直接映射方式,因此虚拟地址的【12:4】位为缓存的行地址,可访问512行,虚拟地址的【31:13】共19位,可作为地址标签。

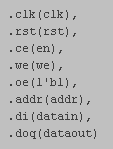

这两个模块其实就是ram,模型可以如下:

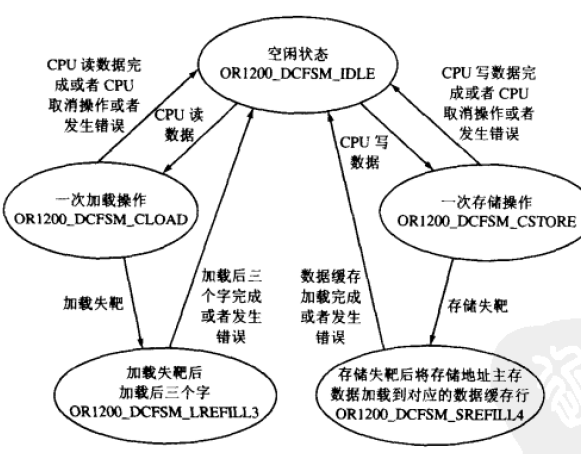

OR1200_dc_fsm模块

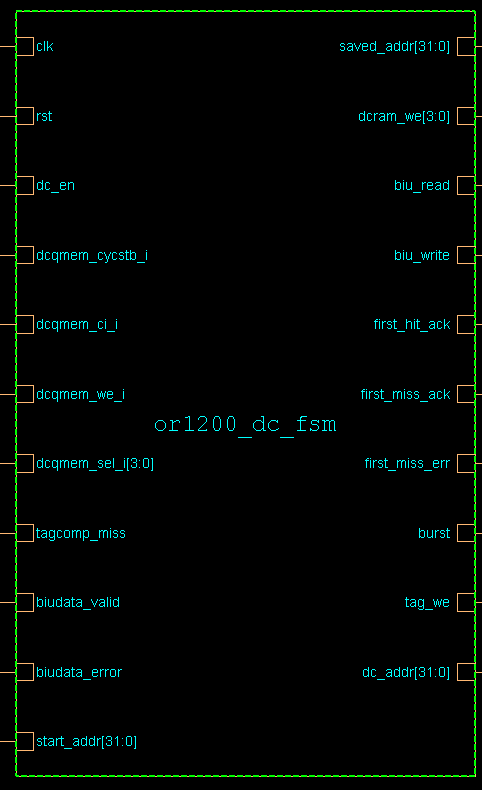

状态切换图如下:

/2

/2

文章评论(0条评论)

登录后参与讨论