四:调试单元

处理器的调试功能帮助软件开发者进行软件调试,通过调试接口,用户可以让处理器在执行到特定的程序时暂停,可以通过JTAG接口将CPU的内部状态读出到软件集成开发环境中。在流水线中,诸如程序计数器PC、存储/装载有效地址(store/load EA)、装载数据、存储数据和当前指令这样的临界信息能够通过调试接口别异步读取到软件集成开发环境中供软件调试。

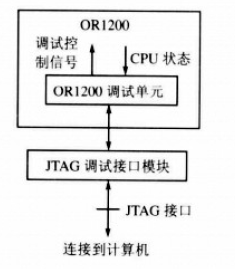

OR1200与调试相关的模块包括OR1200本身的调试单元(debug unit)及外置JTAG调试接口模块。关系可以示意如下:

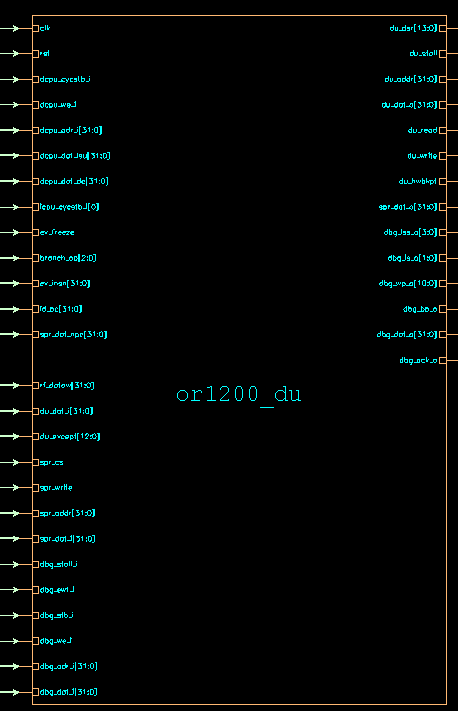

调试接口OR1200_du提供外置JTAG调试接口模块到CPU模块的接口,外部的接口模块通过寄存器控制OR1200_du从而产生控制CPU模块工作的各种信号完成调试目的。

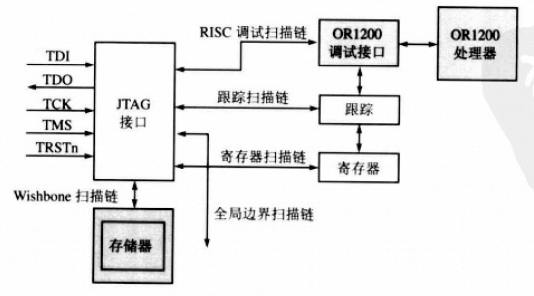

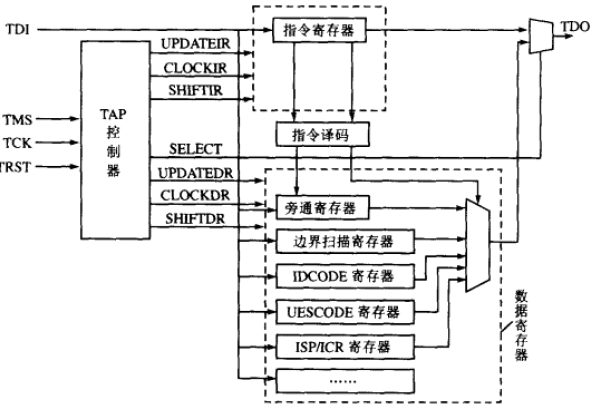

外置JTAG调试接口模块被用来连接OR1200到IEEE1149.1协议的标准调试器,JTAG调试接口模块的框图可如下:

RTL模块框图可以如下:

调试单元是OR1200的一部分,该模块通过监视CPU的取指有效地址EA,加载并存储有效地址和数据信号来控制处理器的运行,从而配合集成开发环境及JTAG接口完成处理器的调试功能。

调试单元在OpenRisc体系结构中是可选择的,专用寄存器UPR(unit present register)的DUP(DUP=6)位若为1,则表示调试单元存在。

调试单元的OR1200-du的调试停止寄存器定义了哪些情况发生时暂停处理器的执行,它能被调试软件通过JTAG调试接口模块编程。处理器暂停后,调试单元的调试原因寄存器定义了哪几个事件引起核心停止程序流的执行并接管开发接口的控制。

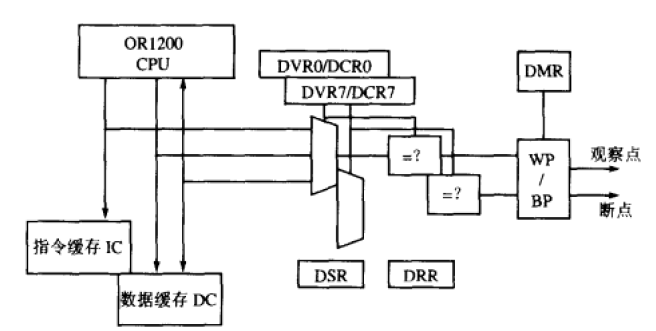

调试单元的结构可以如下所示:

OR1200调试单元的基本特点如下:

1) 定义了8对调试值寄存器(debug value register)和调试控制器寄存器(debug control register)

2) 允许匹配取指有效地址EA、加载、存储有效地址和数据,数据可以是有符号和无符号的数据

3) 允许将匹配条件联合起来实现更加复杂的观察点(watchpoint)

4) 观察点可以产生断点(breakpoint),进而生成自陷异常(trap exception)

5) 观察点的发生次数可以计数后再生成自陷异常

需指出的是,观察点和断点是被匹配编程在调试寄存器中条件的程序或者数据流触发事件。断点与观察点不同,它还挂起当前程序流的执行,并开始断点例外处理。

JTAG开发接口模块

外置JTAG调试接口模块别用来连接OR1200到使用IEEE1149.1(JTAG)协议标准的调试器,JTAG控制器的电路如下:

该控制器主要包括3个部分组成,即TAP(Test Access Port,测试端口)控制器,指令寄存器(包括指令译码器)和数据寄存器。

/4

/4

文章评论(0条评论)

登录后参与讨论