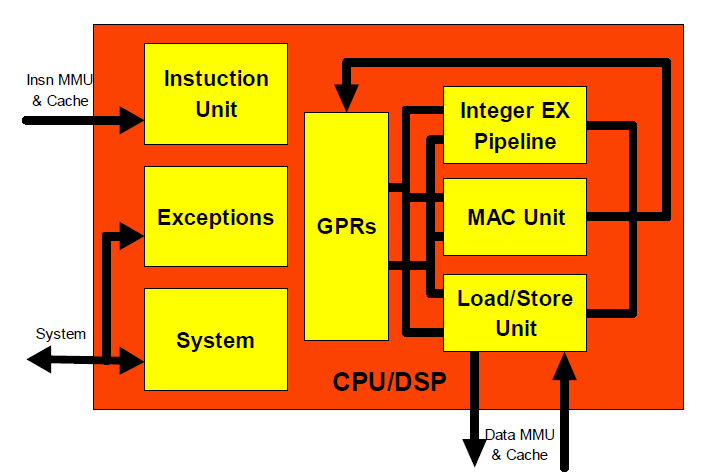

二:CPU/DSP模块

CPU/DSP核心由指令单元(instruction unit)、通用寄存器(GPRs)、异常单元(exceptions)、系统单元(system unit)、整数执行流水线(integer ex pipeline)、MAC单元(MAC unit)、load/store unit(lsu),及它们对应的接口。

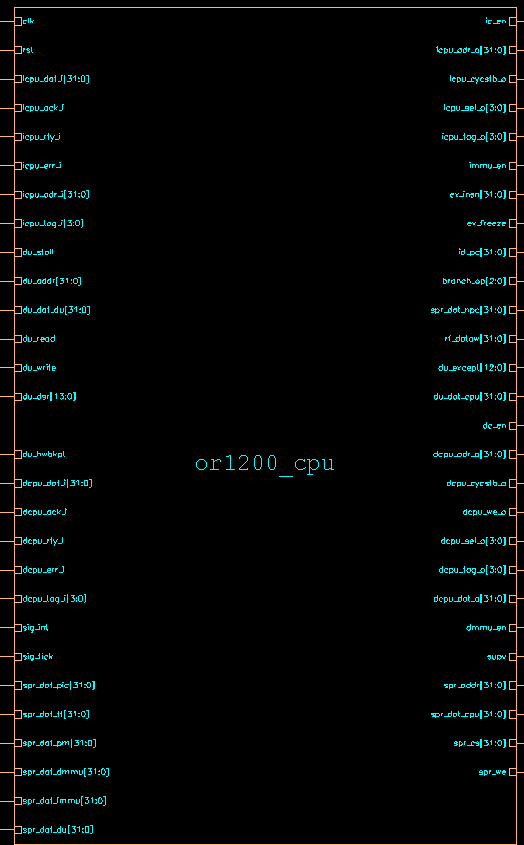

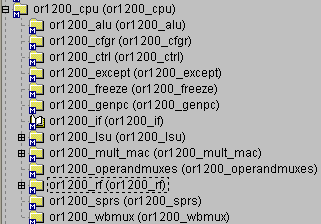

Cpu/dsp单元代码包括如下单元:

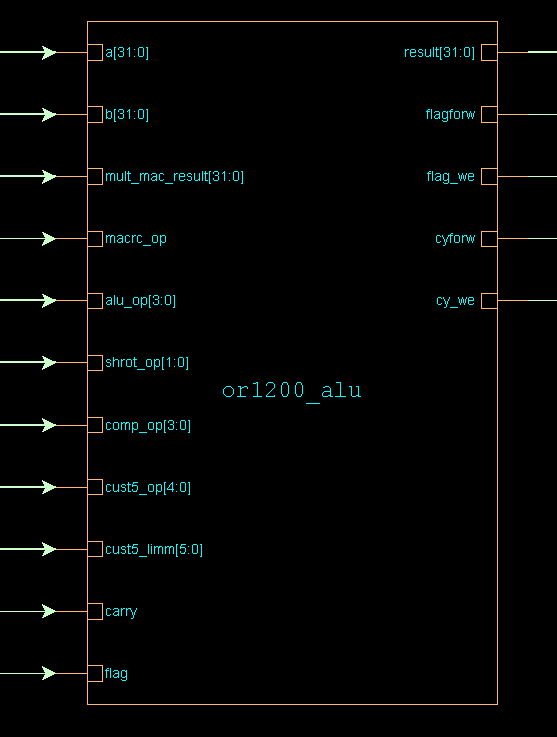

alu模块接收来自ctrl的运算加减及逻辑运算,移位及比较指令,结果反馈到result线上,由wbmux模块选择输出到rf寄存器文件或者输出到operandmuxes,再由lsu模块装入存储器。

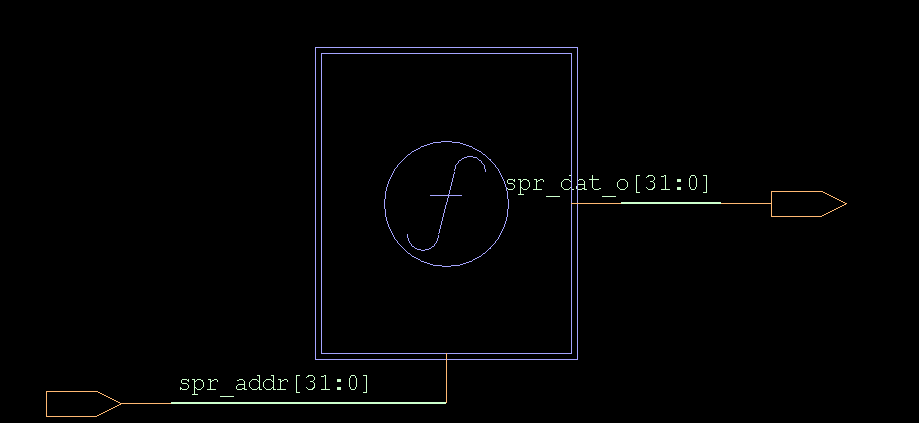

Cfgr从or1200的vr,upr和配置寄存器读出配置值,由spr_addr地址总线上来的地址读出配置寄存器的值,这些值被传送到sprs模块中;

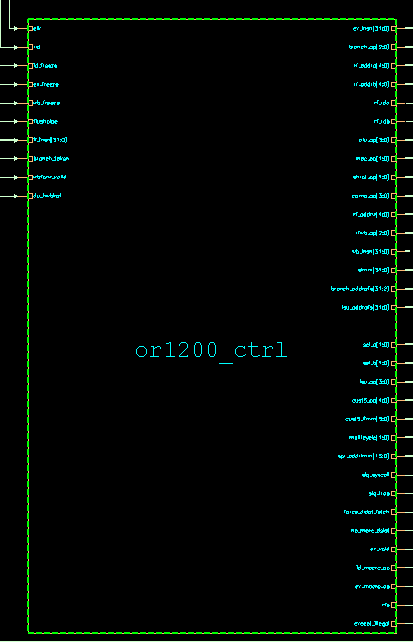

Ctrl模块完成指令解码的大部分工作,它将来自if模块的指令进行分析解码后,分解成rf模块的rama和ramb读地址和读使能信号。

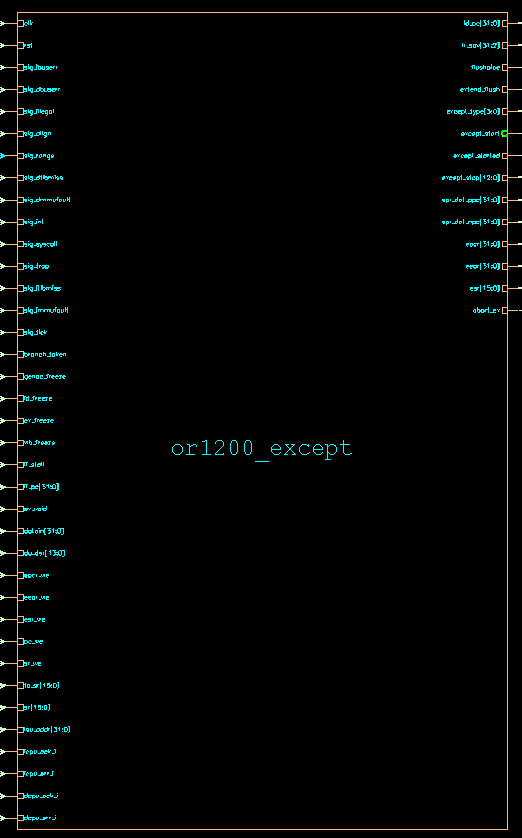

Except模块在一个异常发生后,设置异常类型,将sr寄存器数据拷贝到esr寄存器,将程序计数器地址拷贝到epcr寄存器,将指令出错地址拷贝到eear寄存器。各种异常信号、pc地址及lsu的地址等传入到except模块,该模块触发各种异常,刷流水线,并将异常的各种寄存器值传给sprs模块存储。

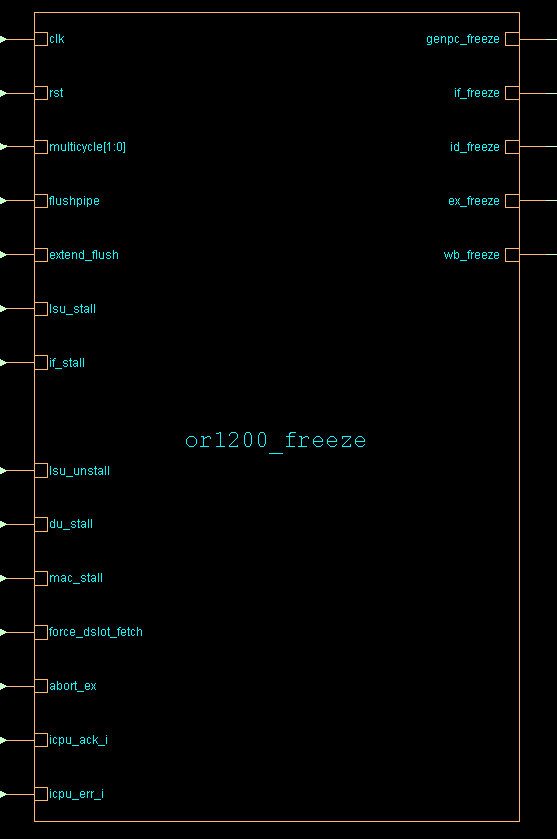

Freeze产生暂停逻辑(停cpu流水线及指令支取等),它根据异常信息、模块停止信息及高速缓存出错信息等产生genpc_freeze、if_freeze、id_freeze、ex_freeze及wb_freeze暂停信号控制流水线中的各个模块。

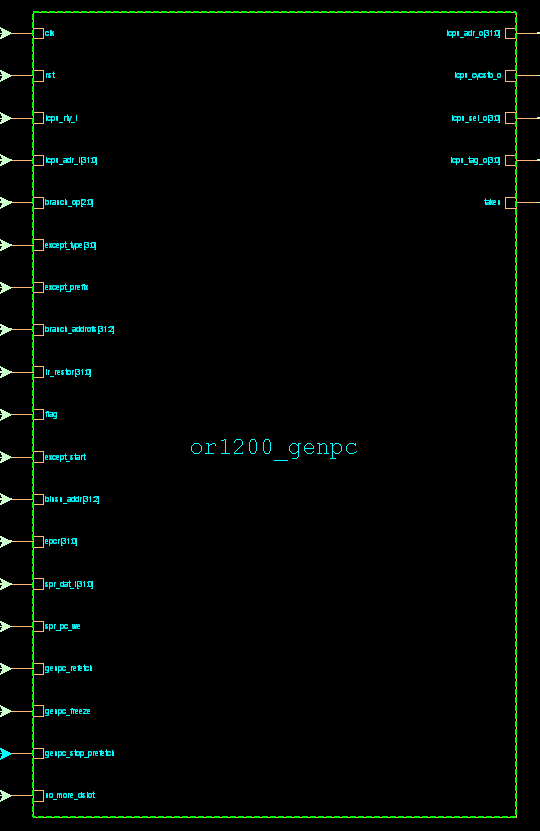

Genpc模块根据分支指令集异常寄存器信息等计算程序计数器pc的地址,并将地址传给指令高速缓存。

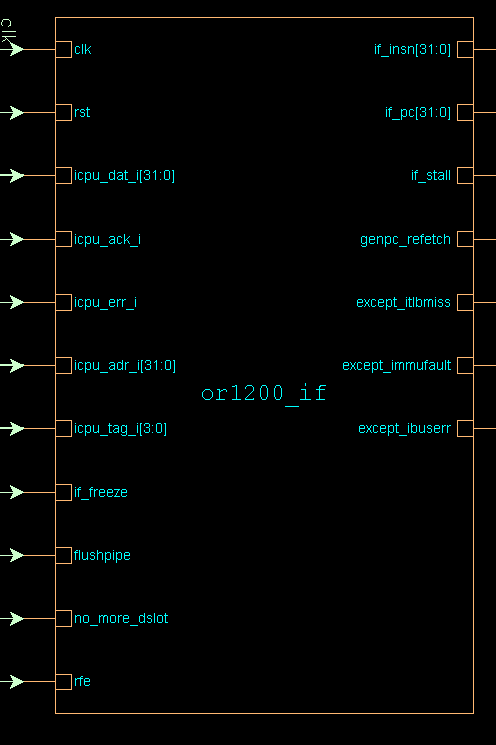

If模块从指令高速缓存中输入指令数据及地址,并将指令分发给ctrl模块解码,将指令地址分发给except模块存储。输出停止信号到freeze和except模块,输出重支取信号到genpc模块,将引起的异常送到cpu内部总线上。

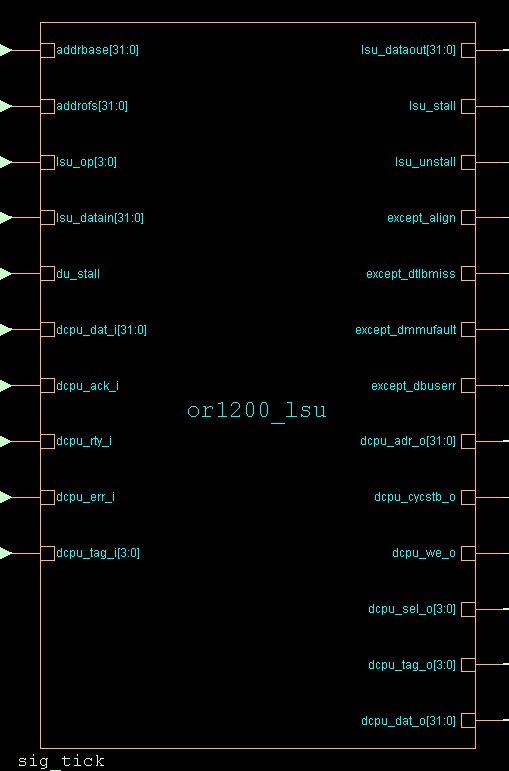

Lsu模块是load/store单元,是cpu和dc之间的接口。

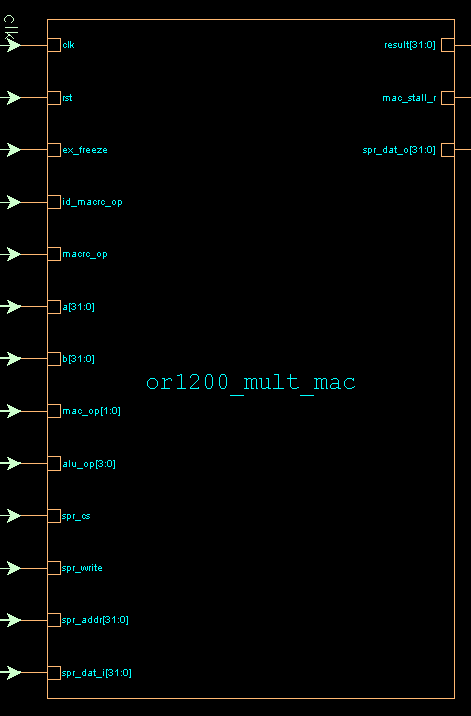

Mult_mac模块是32*32位乘法累加器模块。

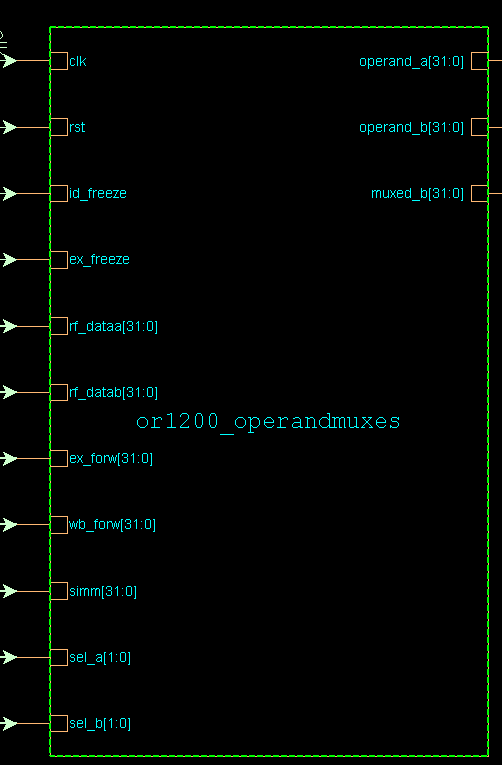

Operandmuxes模块是个操作数多选2的选择器,它从rf模块的数据输出、wbmux模块的数据输出及ctrl模块的simm引脚输出中选择两个数据输出,数据输出a到lsu模块作为基地址,数据输出b作为其他模块的数据输入。

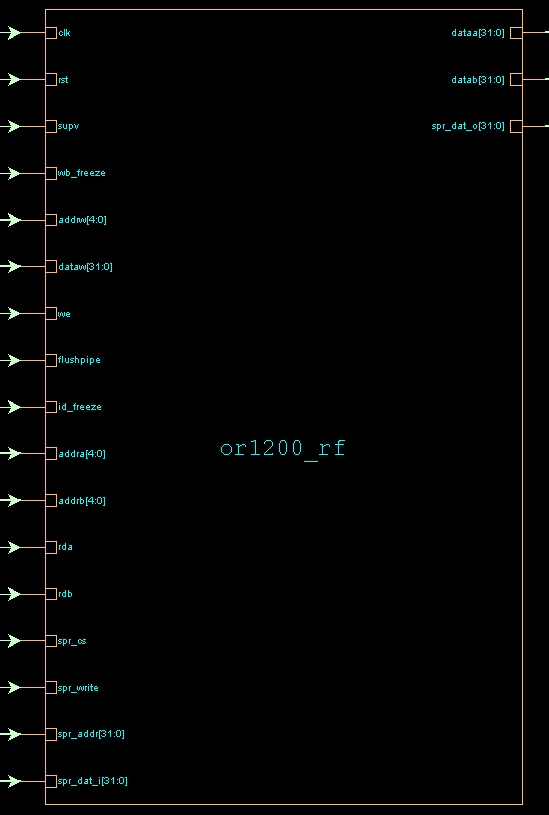

Rf模块是cpu内部的寄存器文件ram,它实例化两个双端口ram或通用寄存器文件ram,将来自wbmux模块的输出的数据和sprs模块输出的数据写入通用寄存器,或将通用寄存器的数据输出到operandmuxes模块或sprs模块。

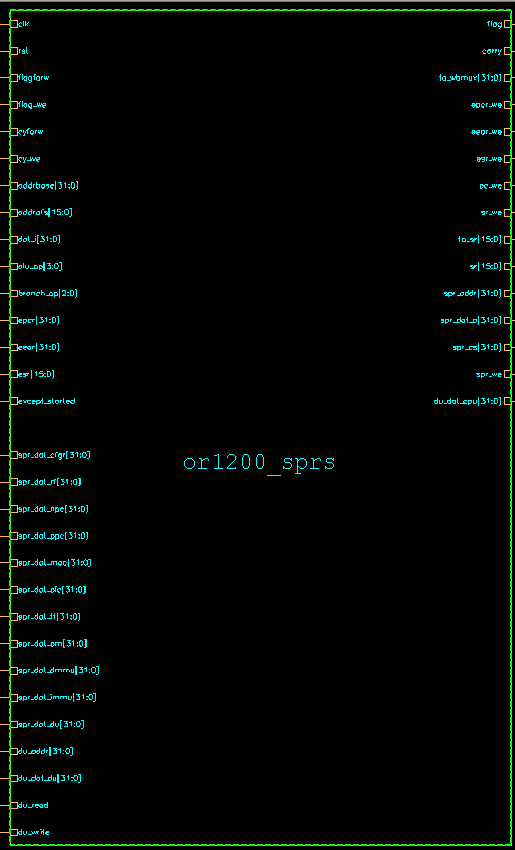

Sprs模块提供了到spr特殊寄存器的即可,它解码spr地址并访问spr。Spr特殊寄存器的数据被输出到各个模块,对各个模块进行控制。

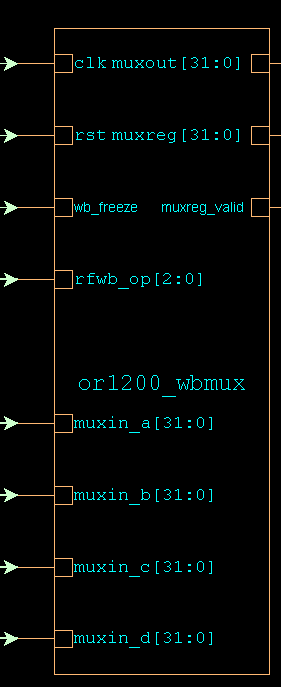

Wbmux模块是or1200的回写复用器,它使用一个4选1的选择器,从4路输入中选择1路进行输出,在流水线回写暂停时,使用rfwb_op[0]设置muxreg_valid输出,这个回写复用器是cpu的流水线的回写阶段。、

/4

/4

用户430155 2014-4-7 09:16