设计思路

1.类Gray码介绍

类Gray码是一种循环二进制码,它们的主要特点是对计数方式加以约束,每次计数时相邻数之间只允许1bit变化,即发生零竞争,从根本上限制了多位同时变化带来的数据的不确定性,类Gray码应用在时序电路中可以防止竞争,以下是十六进制与类Gray码的对比:

2.类Gray码模9递增卡诺图与表达式

由表(2)和表(3)我们不难发现计数器所需的基本单元有反相器,二输入与非门,三输入与非门。

同时需要D触发器,本实验设计了一带清零的DFF,由DFF加上基本门实现模9递增计数。

而运放则需要电容电阻和最基本的MOS管(构成差分对),具体连接则要参看下面的电路图。

1.基本单元

1.数器及反馈放大器

反馈放大器电路图:

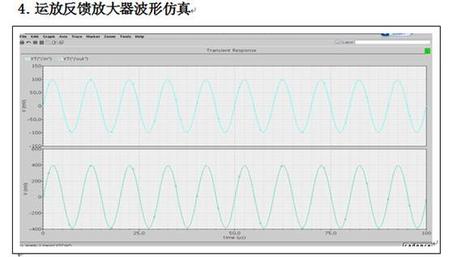

波形仿真

自上而下为D、CLK、CLR、Q、QB,由波形观察知道在时钟上升沿的时候Q状态跳变,变为与D相同的状态,同时在CLR=0时,Q=0;实现了清零的功能。

自上而下依次为Q3、Q2、Q1、Q0、CLK、CLR,由波形看出状态从0000--0001--1001--。。--1111--0000,循环下去,正好是类Gray码的前九个状态的循环递增。同时在CLR=0时,Q的四个状态都为0。

由上图知在输出下降至0DB时的相角约为75°,相位裕量小于180°,运放稳定不会产生振荡,能够保持稳定,电路可以正常工作。

输入信号为幅值为100mv的正弦波,由仿真波形知输出也是正弦波,但是放大了四倍。而由上面反馈放大器电路图的知,放大倍数为1+R3/R4=4;完全正确;其中R3=30k欧,R4=10k欧。

总结体会

1.在制作电路图的时候,也可以进行符号图的制作,但要注意两者的区别与关系,不能混淆;在进行波形仿真时,要注意参数的设置,注意其中的技巧,不然的话,可能不出现仿真结果。

2.在版图绘制过程中,可以通过DRC检查错误,而且错误绝大多数原因是不满足版图绘制的规则,即最小准则;在进行LVS对比时,如果出现结果不相等,多半是因为宽长比不一致造成,这样就要回到电路图或版图中修改参数,直到相等。

3.通过这次实验,掌握了candence软件制作芯片的流程,以及如何写指令,进行DRC及LVS校验。

4.通过这次实验,让我加深了对版图的制作过程的印象,更理解了原先单靠书本学来的知识,与此同时,自己也了解到真正的芯片设计过程是多么的不容易,每一部小错误都会对下面的结果造成不可预测的影响。

5.通过这次实验让自己认识到自己在专业方面的知识还很欠缺,很多时候并不是真正的理解,只是囫囵吞枣似的记忆。

6.这次实验也教会了我做事情要认真,更要有耐心和决心,半途而废是很难把事情做好的。 /5

/5

文章评论(0条评论)

登录后参与讨论