一:设计思路

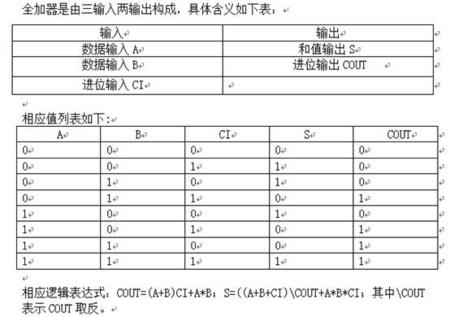

1.一位全加器概念

2.实现四位全加器的思路

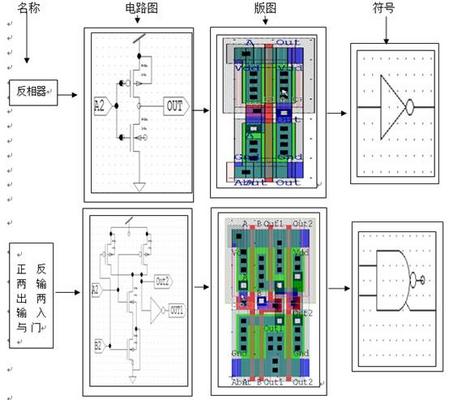

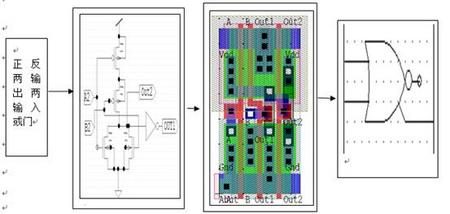

3.基本单元

以上只列出了其中的一部分元件,还有一部分未列出,具体往下看。设计步骤为:先做出电路图,然后制作符号,最后用版图编辑软件,制作出版图。具体步骤在此略去。

二:电路图及波形仿真

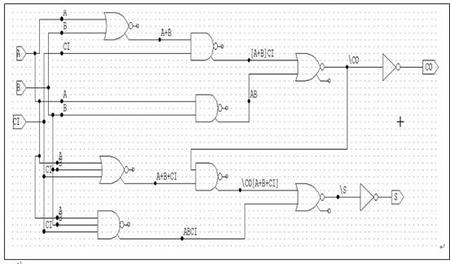

1.一位全加器电路图及仿真

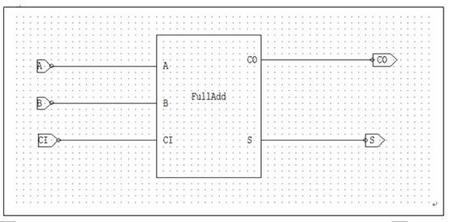

电路图和符号图如下:

上图也体现了具体的实现过程,一位全加器符号图如下:

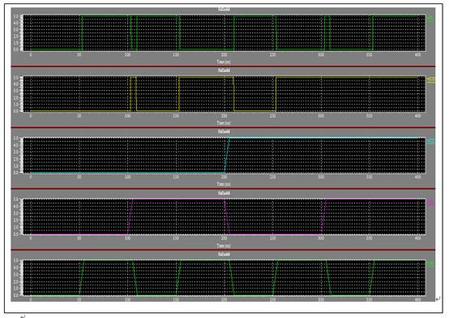

下面是对一位全加器仿真,具体仿真波形如下:

仿真过程中故意设置了延迟,其中从上到下依次为S,COUT,CI,B,A信号,CI,B,A输入的均是脉冲信号,由仿真波形可知所设计的电路是对的。

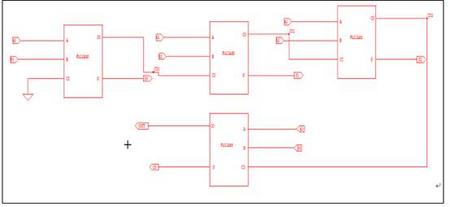

2.四位全加器电路图及仿真

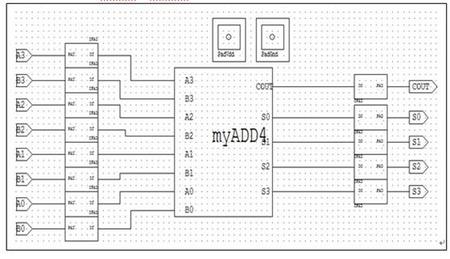

利用一位做出的四位全加器电路图如下:

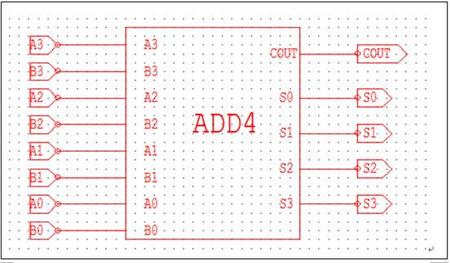

四位全加器符号图如下:

四位全加器波形仿真如下:

同上仿真过程中故意设置了延迟,其中从上到下依次为S0,S1,S2,S3,S4,COUT,A3信号,A3为0111,A2为0110,A1为1101,A0为1000;上图只显示了A3(周期均为50,同时设置了延迟),由仿真波形可知所设计的电路是对的。

三:版图

将IPAD,OPAD,PADVdd,PADGnd引入,电路重新布局,其结果如下:

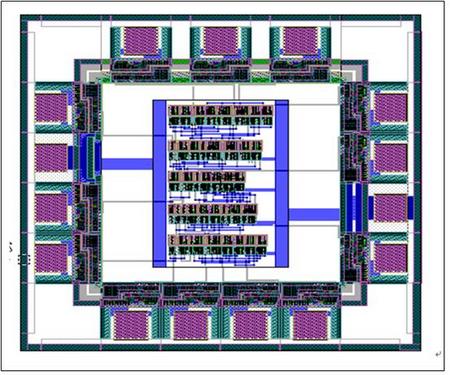

然后再经过一些列的设置,最终通过SPR完成的四位全加器版图如下

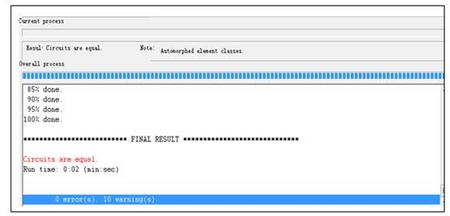

LVS对比电路图与版图,发现两者是相等的,结果显示如下:

上述结果的实现也是要经过一系列的设置,参考书目上都有,在此不做赘述。

四:思考及体会

1.四位全加器可以通过一位全加器的级联,由此可以联想多位全加器也可以进行 同等形式的级联。优点是方法简单,电路简单,缺点是速度低(由于级联而增加 了延迟),故在设计电路时应该折衷考虑。

2.有上述实验的结果可以看出(故意设置延迟的地方),延迟会对结果造成影响,当然有些极短的延迟可以忽略不计,但是大的延迟就会造成结果出错,这一点在设计电路时要考虑到。

3.在制作电路图的时候,也可以进行符号图的制作,但要注意两者的区别与关系,不能混淆。

4.在进行波形仿真时,要注意参数的设置,注意其中的技巧,不然的话,可能不出现仿真结果。

5.在版图绘制过程中,可以通过DRC检查错误,而且错误绝大多数原因是不满足版图绘制的规则,即最小准则。

6.版图的截面图可以查看,这样便于理解绘制版图。

7.在进行LVS对比时,如果出现结果不相等,多半是因为宽长比不一致造成,这样就要回到电路图或版图中修改参数,直到相等。

8.通过这次实验,让我加深了对版图的制作过程的印象,更理解了原先单靠书本学来的知识,与此同时,自己也了解到真正的芯片设计过程是多么的不容易,每一部小错误都会对下面的结果造成不可预测的影响。

9.通过这次实验让自己认识到自己在专业方面的知识还很欠缺,很多时候并不是真正的理解,只是囫囵吞枣似的记忆。

10.这次实验也教会了我做事情要认真,更要有耐心和决心,半途而废是很难把事情做好的。

/2

/2

用户377235 2015-11-3 14:03

用户377235 2015-9-7 11:03

这是什么原因导致的呢?我也碰到了加载不成功,CRC报错的问题了,还没解决好