1、时钟域介绍

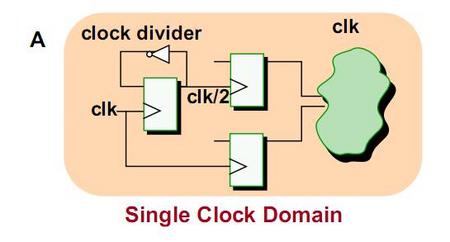

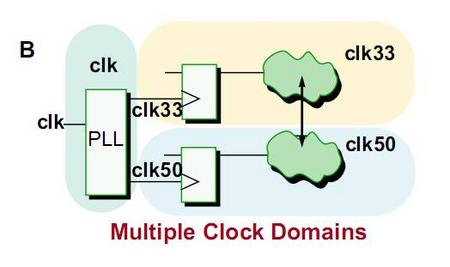

芯片设计中最重要的就是时钟处理,如何处理好时钟的关系成为一款芯片成功的关键。通常来讲将时钟分为同步时钟和异步时钟两大类。

同步时钟:时钟之间有固定的相位关系。

异步时钟:同频不同相,两个时钟的频率是相同的,但是它们之间的相位是不同的;不同频率,两个时钟源不同。

2、为什么要处理跨时钟域

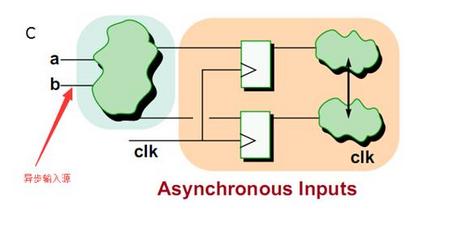

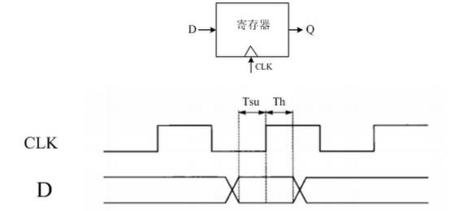

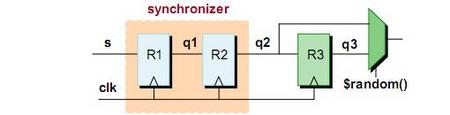

A时钟域的数据传输到B时钟域,被B时钟域的触发器采样到,表面看起来好像没什么问题,整个传输的过程看起来很Happy的样子。可是如果我们时钟无限放大,传输的信号无限放大,自然而然你就会有疑问,会不会传输信号的跳变沿碰到了采样时钟的跳变沿?如果碰到了会出现什么问题,是采样到了0,还是采样到了1?很好,这个问题其实就引出了触发器的setup(建立)时间和hold(保持)时间。

A时钟域的信号传输到B时钟域,无法保证B时钟域触发器的setup time和hold time,这个时候就会出现metastability,也就是所谓的亚稳态,这个亚稳态是芯片设计中最忌讳的东西,它会传播到下一级,甚至引起电路的震荡,危害非常之大。最要命的是亚稳态问题进行仿真的过程中是无法发现的,很多时候是上了FPGA或者芯片回来以后才发现,但是这个时候多半已经晚了。

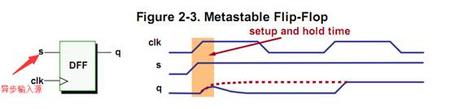

如上图所示,S是异步输入源,在clk上升沿采样的时候,s也发生了跳变,这个时候问题就出现了,q的输出是0还是1,q可能采样到中间值,所以可能随机成0或者1,功能正确不能保证,电路也会偶尔正确,偶尔错误。

上公式给出了亚稳态出现的频率,可以看出它和采样频率,异步数据源的跳变频率,触发器的setup/hold time的window有关。

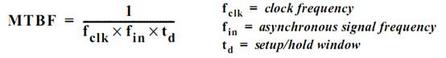

上图示意了当亚稳态发生时真实的电路工作情况和平时的仿真情况,从上图看出,平时仿真和真正硬件工作时的数据可能差一个周期。但是,这些情况是不可预期的,不可预期的东西在芯片上会带来很大的麻烦,譬如芯片正常工作的时候突然挂掉了,你甚至都不知道该怎么debug。

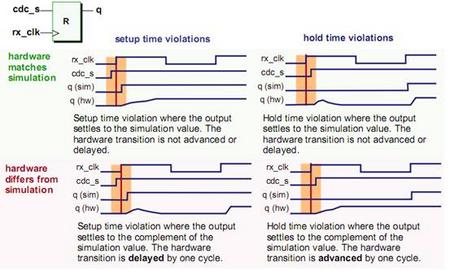

一种模拟亚稳态仿真的方法就是故意随机的插入1T的延时,如下图所示,数据经过同步后再经过随机的mux进行选择,这样可以使仿真更接近实际的工作情况。

/5

/5

文章评论(0条评论)

登录后参与讨论