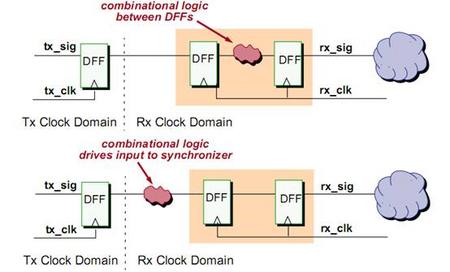

4.1)同步器前不能有组合逻辑电路

如上图,在前一个时钟域的dff输出和后一个时钟域输入之间不能有组合逻辑,原因是组合逻辑会造成毛刺现象,后一级时钟域的dff很可能敲到毛刺,进而引入错误。

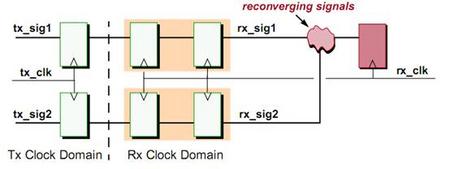

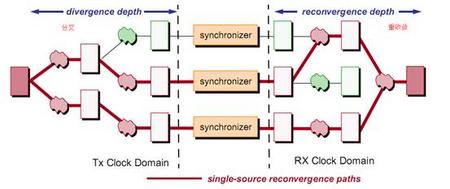

4.2)避免重收敛(reconvergence)和分叉(divergence)

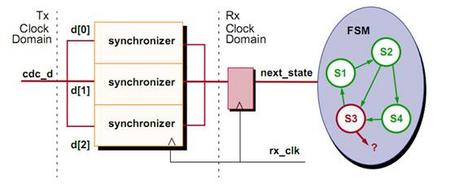

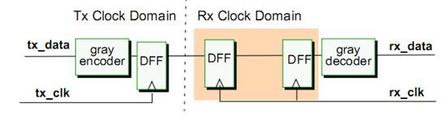

重收敛的含义是,A时钟域的多根信号分别进行同步,同步到B时钟域,然后在B时钟域从新做逻辑汇聚成一根信号。这种同步的方式有一个很大的问题,你无法预期同步后的多根信号和之前还是一致的,例如,两根信号之前都是1,但是在同步后可能变成很多的情况。所以再重新汇聚肯定会出问题。例如下图中的状态机,在A时钟域可能是S1状态,但是同步后可能就变成了S2状态了。其实重收敛的问题可以避免,就是采用格雷码编码,避免一个时刻多个数据跳变。

如下图的格雷码编码再解码,就可以解决上述的一些问题。

分叉的含义与之相反,在A时钟域的单根信号被分别同步到B时钟域的多根信号,这同样会面临同步不一致的情况,有的被同步成1,有的被同步成0。

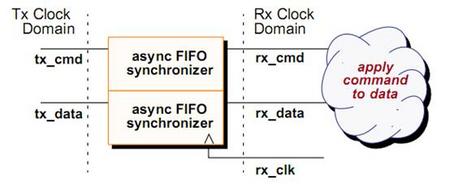

4.3)避免将cmd和data分开进行同步,而要绑定到一块采用异步fifo实现

Cmd和data经过异步fifo处理后的延迟可能会发生变化,所以应当避免将他们分开进行同步,而要绑定到一块进行同步{cmd,data}。

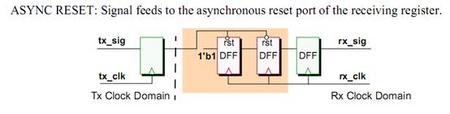

最后提一下异步复位同步释放电路,这种电路在soc中也广泛被使用。

/5

/5

文章评论(0条评论)

登录后参与讨论