6、false 路径

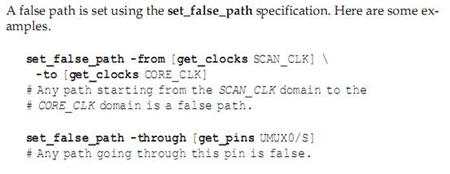

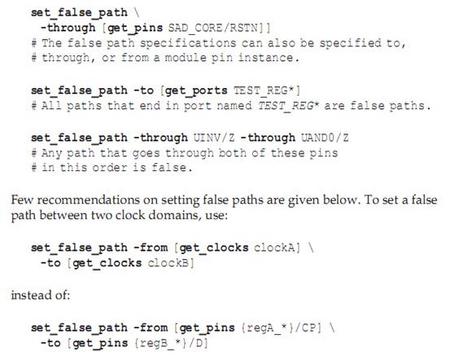

硬件设计中总是会存在一些不可能的逻辑电路路径,这一种路径需要设置成false path,目的是让工具不再对其进行优化和时序检查。比较常见的false path例如两个时钟域之间的逻辑,如果你不指定为falth path,那么工具费很大的力气也很难让时序满足,因为本身跨时钟域时序关系就是不确定的。关掉的目的就是不让工具检查,省时省力,而他们之间的正确性要靠cdc处理(可以参考我之前写的关于cdc的 处理方法)。另外还有scan逻辑和正常逻辑之间的逻辑也可以设置成false path。

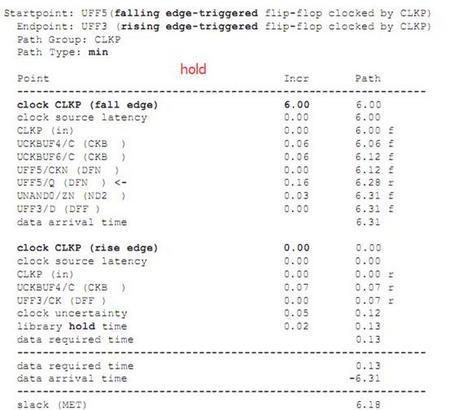

7、half cycle path半周期路径

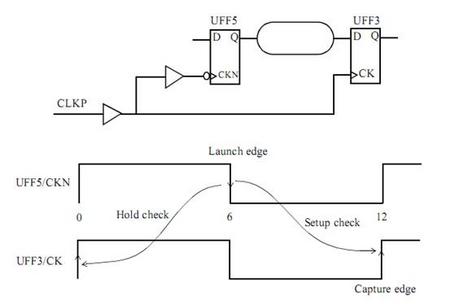

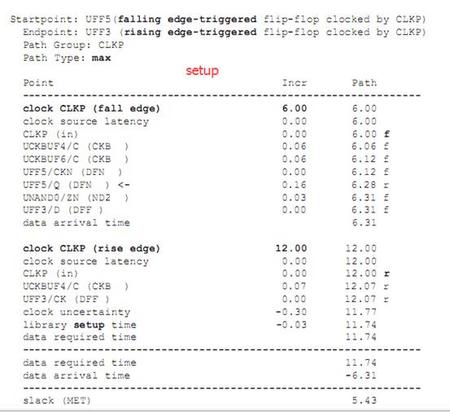

有一些外设的工作沿是双沿的,也就是一个边沿推出数据,另一个边沿采样数据,比较常见的外设有ddr,也有一些通信协议,例如xgmii用于以太网和光纤的通信协议。

如上图,下降沿launch数据,最靠近的上升沿capture数据,离capture边沿1T的是hold检验边沿。这样的话,可以看成hold多了半个周期的slack。

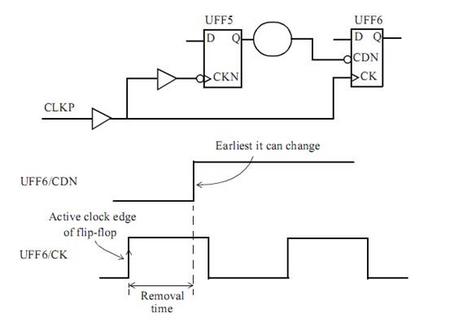

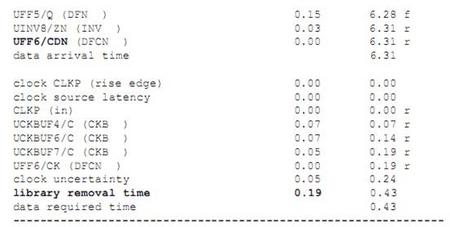

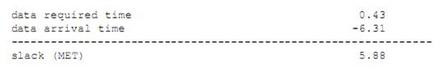

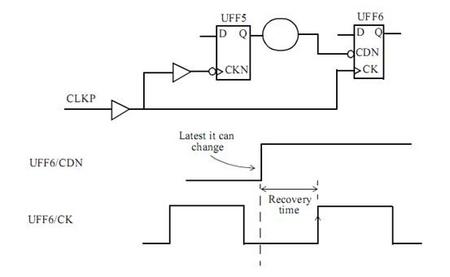

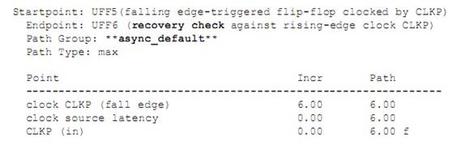

8、recovery和removal

这两个的时间检查用于异步逻辑的释放动作,例如异步的复位动作。Removal类似于hold的检查,recovery类似于setup的检查。

/4

/4

文章评论(0条评论)

登录后参与讨论