一、研究生期间,开始想学习IC设计,所以开始学习FPGA设计项目。不过目前还在犹豫是学习IC设计前段还是后端。这里将遇到的问题和方法整理成一个博客,以便其他人的学习。

现在就开始一步步入手ModelSim,并通过与Quartus无缝衔接实现仿真。后面将写Modelsim-Atera的仿真过程,不是很一样。本文使用了ModelSim10.0c + QuartusII 10.0,其他版本基本雷同,请自行研究。

看不清图的点开看大图!

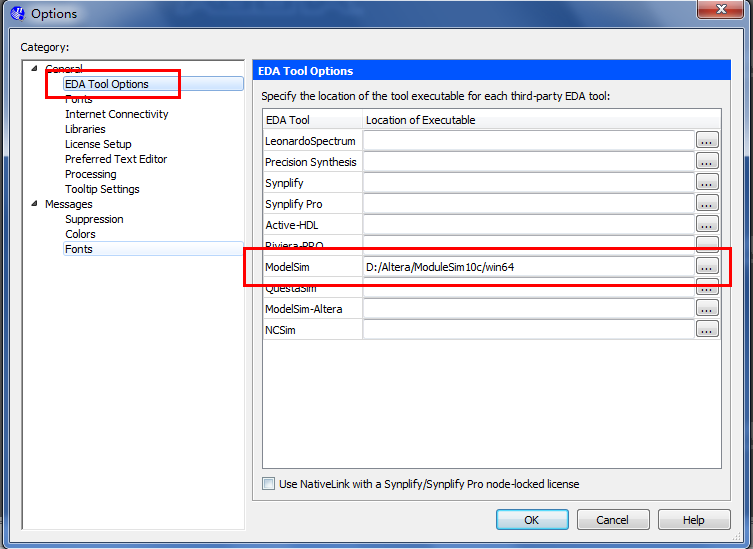

1.设置第三方EDA工具

在Tools -> Options中设置ModelSim的安装路径,注意要设置到win32文件夹(64位软件对应的就是win64)。

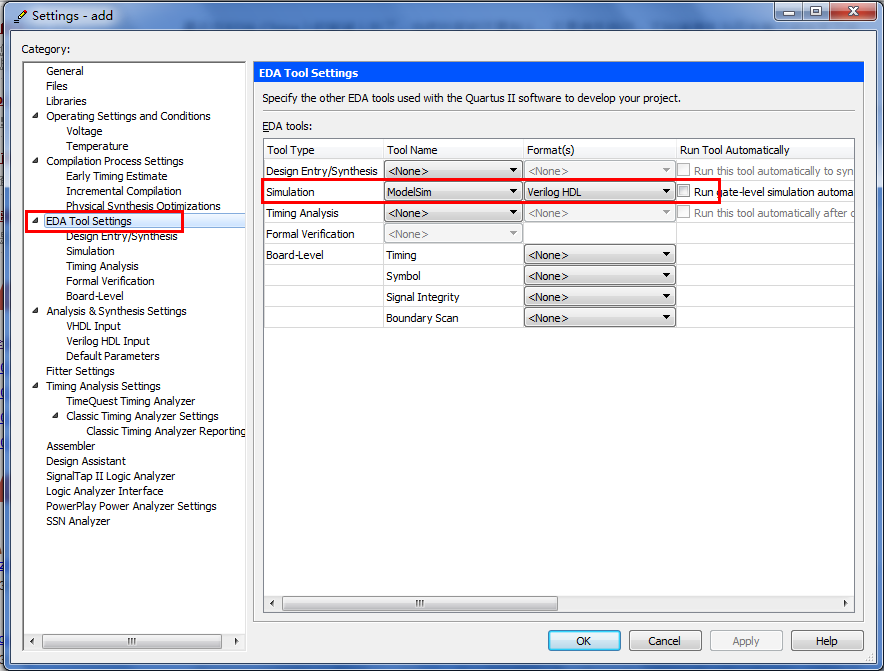

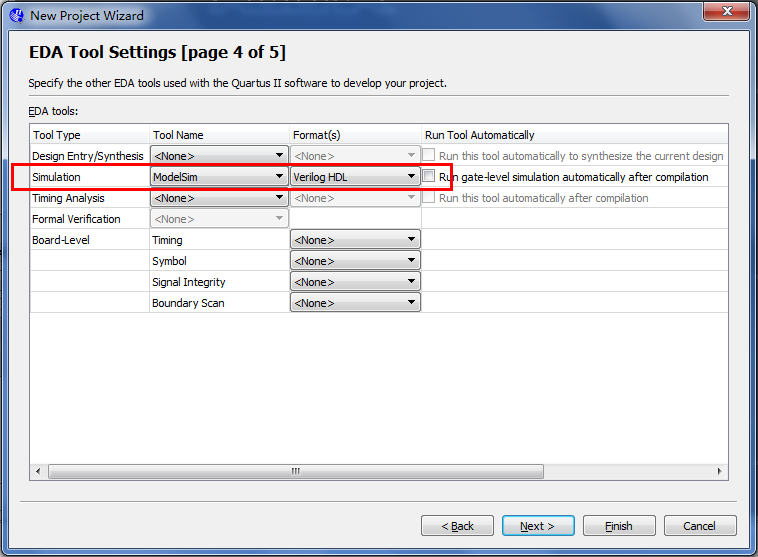

建立一个工程(依然以加法器为例)。在Assignments -> Settings中设置仿真工具为ModelSim。这样Quartus就能无缝调用ModelSim了。

当然也可以在建立工程的时候就设置仿真工具。

2.编写Testbench

说到Testbench,你可以叫它Testbench,或者Testbenches,但不是Test Bench。说起来,就连Quartus也没注意这个问题,至于原因嘛参见Common Mistakes In Technical Texts一文。文章中还列举了些别的错误用语,包括Flip-flop不能写成Flipflop,等等。文章链接:

http://www.sunburst-design.com/papers/Technical_Text_Mistakes.pdf

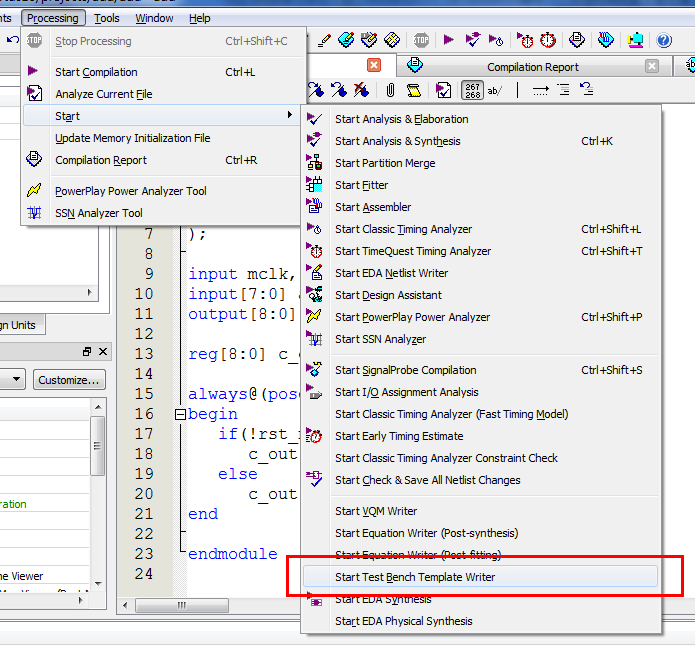

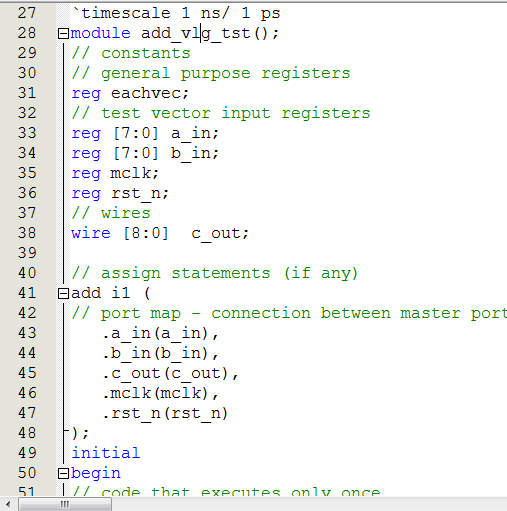

我们可以通过Quartus自动生成一个Testbench的模板,选择Processing -> Start -> Start Test Bench Template Writer,等待完成后打开刚才生成的Testbench,默认是保存在simulation\modelsim文件夹下的.vt格式文件。

打开vt文件后可以看到Quartus已经为我们完成了一些基本工作,包括端口部分的代码和接口变量的声明,我们要做的就是在这个做好的模具里添加我们需要的测试代码。

一个最基本的Testbench包含三个部分,信号定义、模块接口和功能代码。

‘timescale 1ns/ 1ps表示仿真的单位时间为1ns,精度为1ps。想要进行仿真首先要规定时间单位,而且最好在Testbench里面统一规定时间单位,而不要在工程代码里定义,因为不同的模块如果时间单位不同可能会为仿真带来一些问题,而timescale本身对综合也就是实际电路没有影响。

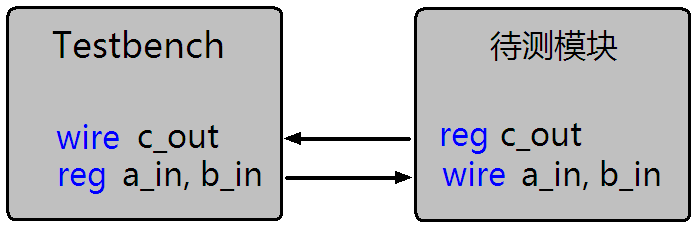

其实Testbench本身可以看做一个模块或者设备(本例中的模块名为add_vlg_tst),和你自己编写的模块进行通信。通过Testbench模块向待测模块输出信号作为激励,同时接收从待测模块输出的信号来查看结果。因此,在待测模块中的reg型信号在Testbench中就变成了wire,待测模块中的wire型信号在Testbench中则对应为reg型。那么inout怎么办呢,inout型信号也要设成wire,同时要用一个reg型信号作为输出寄存器,同时设置一个三态门,由一个使能信号控制,如:assign inout_sig = out_en ? out_reg : 1’bz;

处理完接口和声明之后,需要自己设置一些激励信号,激励信号的内容就是肯能会输入到待测模块中的波形。下面我们就来写一个简单的测试程序。

首先需要一个复位信号:

initial

begin

rst_n = 0;

#100 rst_n = 1;

end

initial开头的这个过程在Testbench中只执行一次,#100表示延时了100个时间单位,我们之前已经通过timescale进行了设置,这里延时了100ns。这就有点类似于C语言了,代码通过延时被顺序执行,rst_n在0时刻为低电平(也就是逻辑0),100ns后变成高电平,从而形成了一个上电复位。

其次是时钟,使用always模块来完成:

initial

begin

mclk = 0;

end

always

begin

#10 mclk = ~mclk;

end

always模块中的代码会不断重复执行,利用这个特点,每10ns翻转一次mclk,只是这样还不行,还要给mclk一个初值,就是上面的initial语句。如此便可以生成一个周期为20ns,频率50MHz的方波信号,作为本例的系统时钟。

当然,这个时钟也可以通过initial模块实现。只需添加一个while(1),即死循环。

initial

begin

mclk = 0;

while(1)

#10 mclk = ~mclk;

end

Testbench中的很多操作都是不可综合的,同时它的风格也可以比较随意。

设置完时钟和复位,就需要设置输入信号:

initial

begin

a_in = 1;

b_in = 3;

#200 a_in = 2;

b_in = 0;

#200 a_in = 3;

b_in = 3;

end

注意这里a_in = 1和b_in = 3是同时发生的,也就是并行的,之后延时200ns,a_in = 2同时b_in = 0,如前面所说,想要实现顺序操作,就需要使用延时,如果两个语句间没有延时,就表示同时执行。还有一点,这个initial语句块和负责复位的initial语句块也是并行的,并且都是从0时刻开始。也就是说,0时刻后经过100ns rst_n复位,再经过100ns(从0时刻起),a_in = 2被执行。

至此,测试程序也完成了,让我们开始仿真吧

3.设置Quartus并调用仿真工具

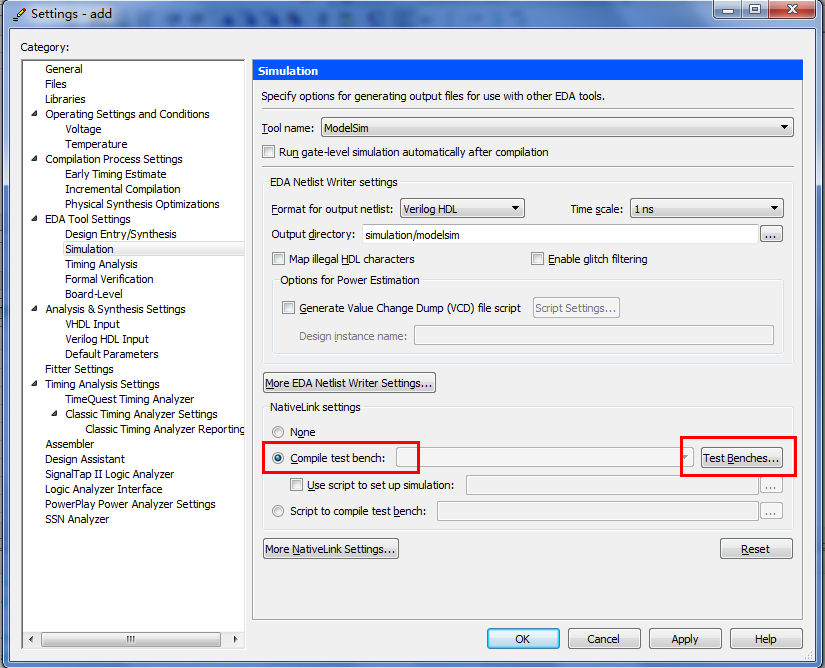

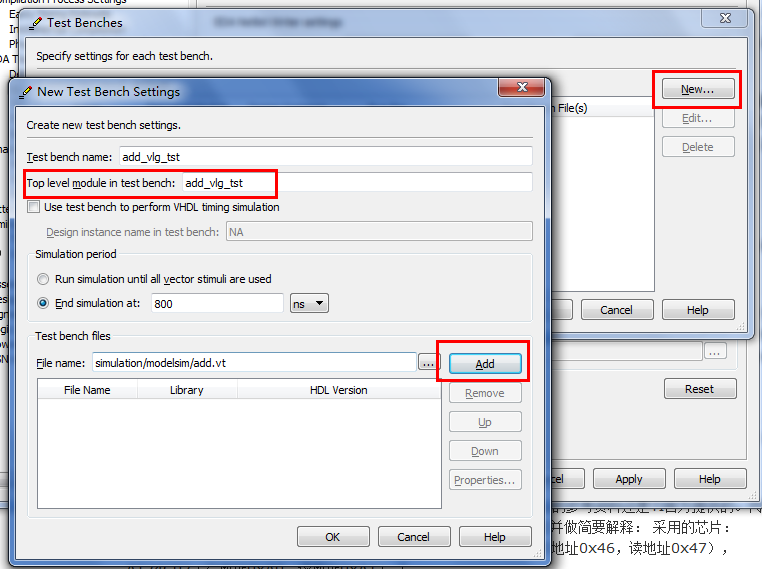

运行仿真之前,还要设置一下。在Simulation选项卡中配置仿真选项,可以配置仿真语言、仿真时间的格式以及输出目录。选中mpile test bench,点击Test Benches打开Test Benches对话框。

点击New新建一个Test BenchSetting,填入Testbench模块的名称(这里是add_vlg_tst),酌情设置仿真运行的时间(这里设为800ns,只是进入ModelSim后仿真自动执行的时间,不设或随意设置也行),并将刚才编写的Testbench添加进来。

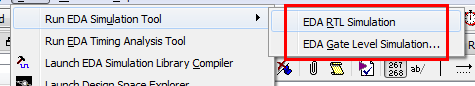

一路OK后,选择Tools -> Run EDA Simulation Tools,有两个选项,RTL Simulation是RTL行为级仿真,只验证功能是否正确,与在哪个芯片上运行无关,仿真前至少需要执行一次Analysis&Synthesis;Gate Level Simulation是门级仿真,涉及到具体的芯片,并且仿真前需要编译工程,在门级仿真中ModelSim会将布局布线后的门级延时体现在波形中,在测试一个具体的工程模块时,应当先进行RTL仿真,之后还要进行门级仿真。

4.ModelSim工具的基本操作

运行RTL Simulation进入ModelSim界面。在这里介绍几个比较重要的部分。

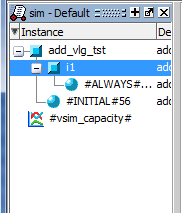

在view菜单中,可以显示和隐藏各种工具窗口。其中Structure窗口显示了测试模块和待测模块的结构:

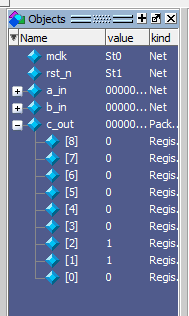

点击不同的模块,在Objects窗口中可以查看选中模块中的信号,因为除了端口(port)以外,还有很多内部信号默认是不显示波形的,通过将需要的信号拖到Wave窗口中,就能够显示。

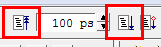

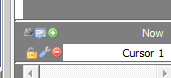

工具栏中的  部分是用来控制仿真运行的,左侧红框中的是复位,在文本框里设置要执行的时间,点击右侧红框中的按钮就可以执行了。其他的请自行摸索或参看Help文件。

部分是用来控制仿真运行的,左侧红框中的是复位,在文本框里设置要执行的时间,点击右侧红框中的按钮就可以执行了。其他的请自行摸索或参看Help文件。

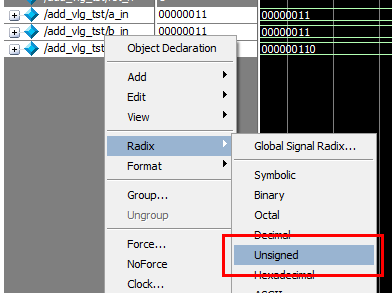

如果面对一大堆0101感觉很晕,可以在信号列表里选中信号,右键选择要显示的数据格式。

而Wave窗口的左下角有几个小按钮,是用来设置游标的,通过添加游标,可以测量相应的时间,也可以在这里配置时间刻度的格式。

在Wave波形图中,使用滚轮和鼠标右键可以很方便的缩放或选择波形区域,下图就是这个全加器工程的波形图,在复位之后,c_out的值等于a_in与b_in的和,并在时钟上升沿输出。

二、使用Modelsim-Atera进行仿真过程

软件使用版本:Quartus II 13.0+Modelsim_Altera10.1d

工程使用例程:tcd1209+ad9945,verilog HDL设计

仿真选择:时序仿真

撰写人:Strive_JP

一、开始前的准备:

时序仿真即后仿真,是利用SDF文件对原有设计进行时序标注之后,再进行仿真。时序仿真可以反映设计的时序性能,使设计接近于真实情况。Modelsim本身不可以产生时序仿真所需的SDF文件,但可对EDA工具如QuartusII 生成的SDF文件进行仿真。仿真前,首先需要用quartusII 生成用于功能或时序仿真的网表文件.vo),以及使用EDA 仿真工具生成时序仿真所需的延时输出文件(.sdo)。

二、时序仿真流程

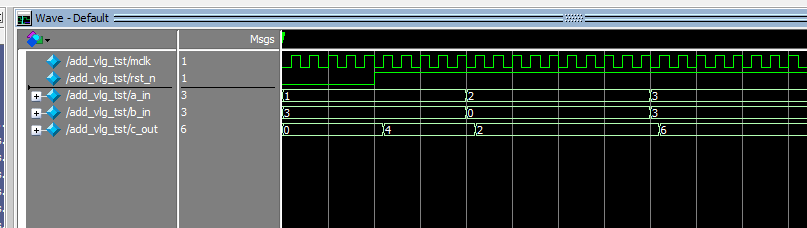

1、设置modelsim仿真路径,打开quartus II工具,选择菜单栏下面的tools option选项,打开如下界面。

2、在EDA Tools Options里面设置好Modelsim_Altera的路径。其实现在quartusII版本较高,与Modelsim_Altera都是一起安装的。这一步基本已经做好。

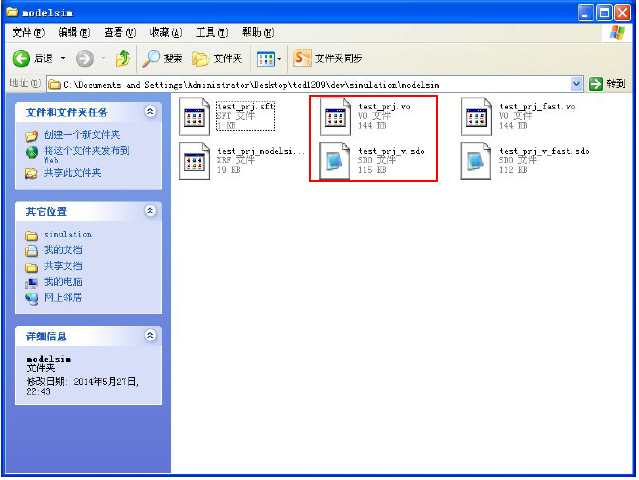

3、打开QuartusII工程文档。进行RTL设计,编译、综合完成后,生成所需的.vo和.sdo文件,生成的文件在quartusII 工程目录的simulation文件夹里面。这里以项目过程中一个例子来说明。生成的工作路径中文件如下所示。

4、接来这一部分非常重要,也是Modelsim-altera软件不同于以往的Modelsim软件重要的一步。将仿真过程中用的的库文件复制到上面文件夹中(必须放在此文件夹中,否则无效)。在本例程中只用到了器件库,CycloneII。因此只需将编译好的cyclone库文件拷贝到该文件夹中。库文件路径为:D:\Altera\13.0\modelsim_ase\altera\verilog\cycloneii。即安装路径下面的子路径。当然也可以在Modelsim-altera中新建库文件,编译所需要的库,之后再将库文件拷贝至此目录下。

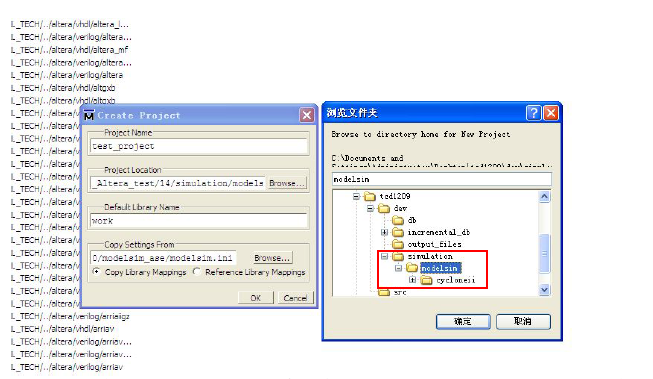

5、打开Modelsim-Altera,新建工程。工程路径同样也指向modelsim文件夹下面。如下图所示。

6、添加文件至工程,由于进行时序仿真,故这里面添加.vo和testbench文件。全编译完成后,开始继续下面的仿真。

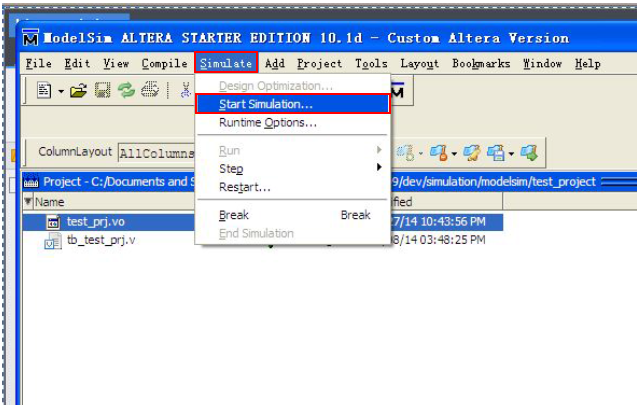

7、在功能仿真中,我们通常只需要输入vsim testbench就能执行仿真。但是时序仿真需要指定库路径和.sdo文件。万万不可像功能仿真那样了。选择菜单栏的simulate。

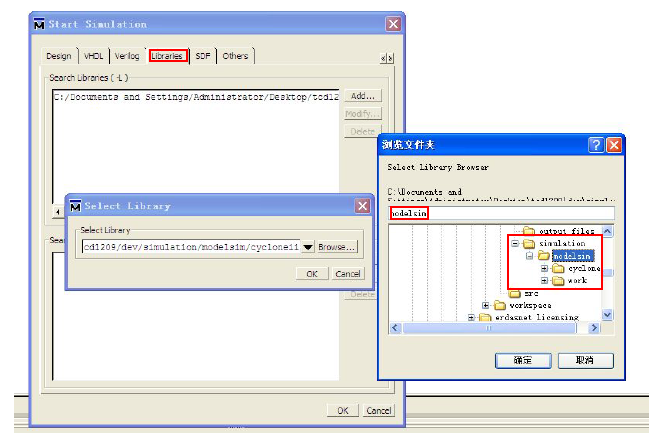

8、进入start simulation界面,在Design窗口的work库中选择testench模块。切换到libraries界面,增加modelsim文件夹里面的cycloneII库至libraries里面。如下图所示:

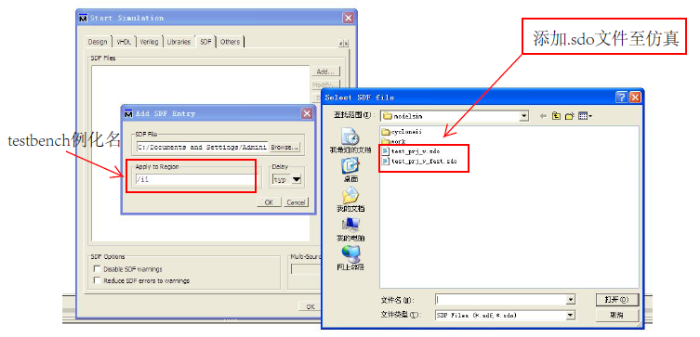

9、库文件增加完成后,切换至SDF窗口,增加.sdo文件,在Apply to Region窗口中输入testbench的例化名(这点很重要,注意是例化名)。

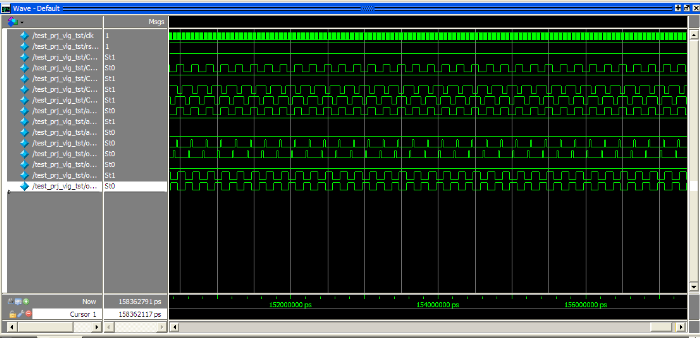

10、点击一系列的OK之后,Modelsim-Altera自动进入仿真界面。增加波形至wave窗口,运行run,完成仿真。

这样,利用Modelsim-Altera采用GUI进行时序仿真的流程就此结束。

三、Modelsim-Altera时序仿真过程中调用四种常用的仿真库,分别为:

·元件库,例如本例程所用到的cycloneII元件库,根据FPGA特定的型号。

·altera_mf,调用Megafunction的设计仿真时需要;

·lpm,调用lpm元件的设计仿真时需要;

·primitive库,调用altera的原语(primitive)设计仿真时需要;

Modelsim在仿真过程中,工作库只能有一个,而资源库则可以有多个。Modelsim-Altera在安装后,安装目录下已经默认安装很多库,在仿真的时候拷贝到仿真目录下即可直接调用。资源库是不变的,而工作库是用来把不同设计的编译文件放进去,且根据需要,不断更新。

/2

/2

文章评论(0条评论)

登录后参与讨论