随着5G通信、自动驾驶及物联网等新兴应用的发展,图像处理、AI算法加速、软件无线电等复杂多任务设计越来越挑战嵌入式平台的处理能力。赛灵思推出的真正 All Programmable (全可编程)异构多处理 SoC——Zynq UltraScale+MPSoC,相比Znyq7000系列每瓦性能提升5倍,它集成了四核Cortex™-A53 处理器,双核 Cortex™-R5 实时处理单元以及Mali-400 MP2 图形处理单元及 16nm FinFET+ 可编程逻辑相结合的异构处理系统。米尔科技推出的MYD-CZU3EG开发套件搭载的就是UltraScale+ MPSoC平台器件 — XCZU3EG,具有高性能,低功耗,高扩展等特性,除了这款异构SOC之外,板子还搭载了丰富的接口和完善的开发资料,可以帮助开发人员降低产品开发周期,实现产品快速上市。

以下是笔者实际操作的流程:

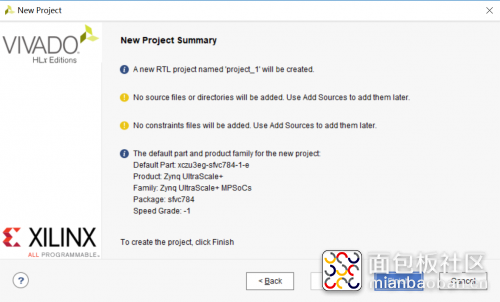

(1) 新建vivado工程

创建一个RTL工程,选择开发板芯片为 xczu3eg-sfvc784-1-e。

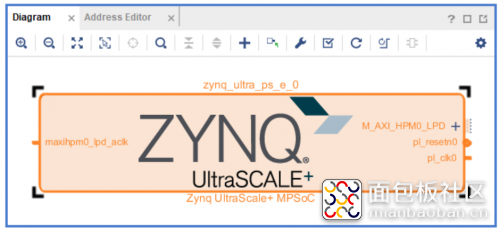

(2)创建Block Design,添加并配置PS 的IP核

单击 IP Integrator->Create Block Design 新建一个 Block Design,点击Add IP,添加Zynq UltraScale+MPSoC IP核

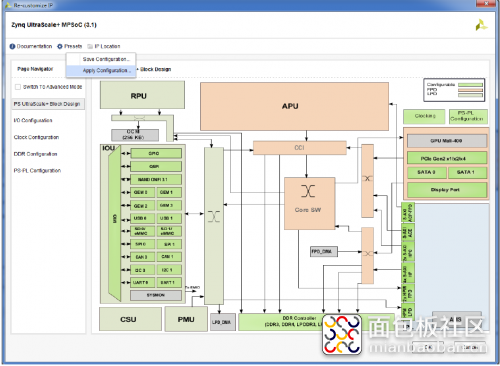

双击zynq mpsoc 核导入配置文件Presets‐‐>Apply Configuration

zynq mpsoc 核导入配置文件

厂家在光盘资料中提供了示例预配置文件,导入hello_world.tcl 配置文件,然后点击OK。

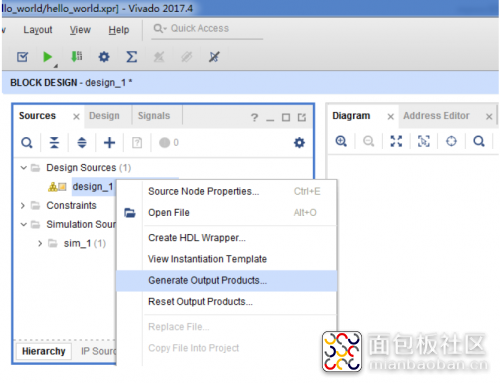

(3)生成综合文件

右击 design_1‐>Generate Ouput Products‐>Generate

生成综合文件

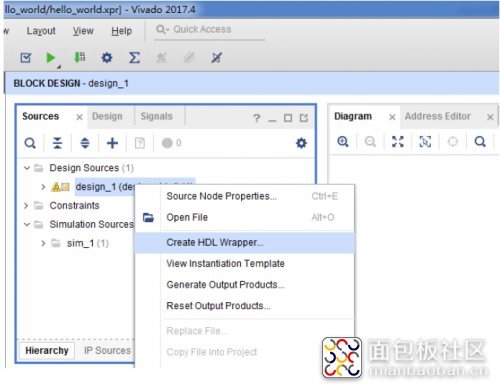

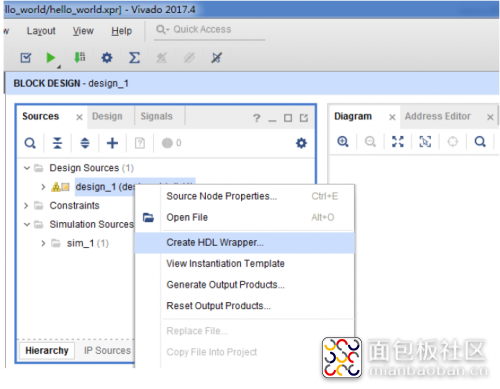

(4)生成FPGA顶层文件

(5)生成bitstream

(6)导出硬件配置文件

点击菜单栏上的 File‐>Export‐>Export Hardware‐>OK 导出硬件配置文件

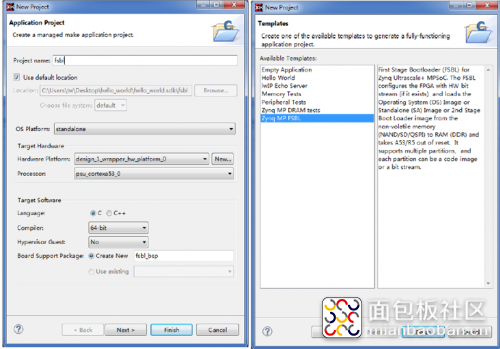

(7)启动SDK,新建fsbl

点击菜单栏上的 File‐>Launch SDK‐>OK 启动 SDK

在Xilinx SDK软件中,点击File‐‐>Application Project 新建工程,输入工程名为fsbl,选择Zynq MP FSBL,点击Finish。

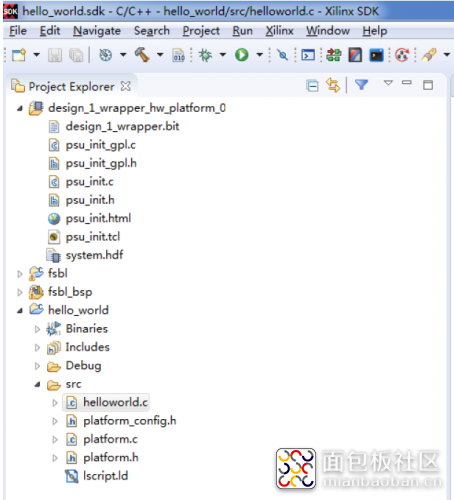

(8)新建一个helloworld工程

在Xilinx SDK中点击File‐‐>Application Project 新建工程,输入工程名为hello_world,选择Board Support Package为上一步中生成的fsbl_bsp,选择hello_world 模板,点击Finish。

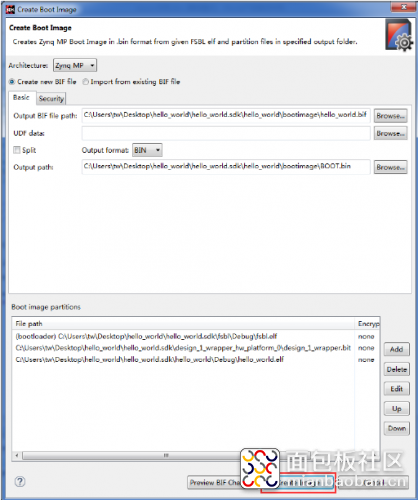

(9)生成boot image

右击 hello_world ‐‐>Create boot Image,点击Create Image,生成BOOT.bin 启动文件

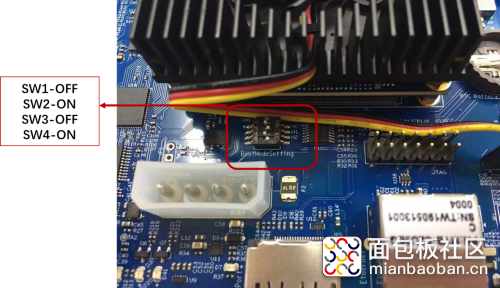

将开发板的启动模式switch 开关SW1 的1 拨到OFF,2 拨到ON,3 拨到OFF,

4 拨到ON,设置成TF 卡启动模式,

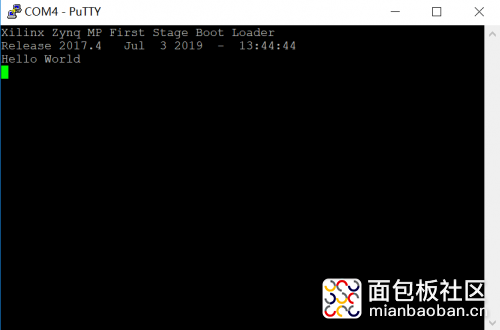

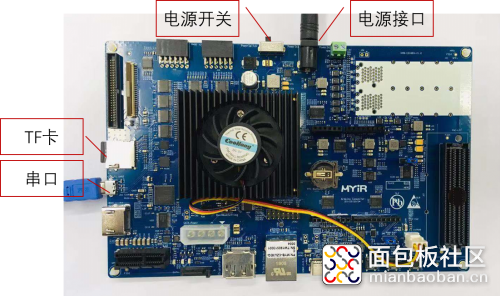

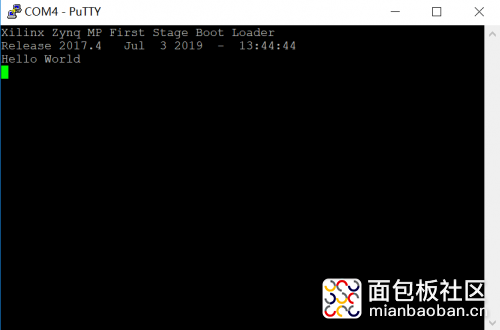

然后将这个BOOT.bin 文件拷贝到SD 卡,板子接入电源,串口连接电脑,打开电源开关,开发板上运行。电脑端连接microUSB线,打开putty,可以板子上电运行在终端打印字符“”“Hello World”

总结

作为国内首款Zynq UltraScale+ MPSoC平台开发板,MYD-CZU3EG核心板性能配置强大且设计紧凑可靠,外设底板接口资源丰富,厂家为开发者提供的软件开发环境也比较完善,非常适合人工智能,工业控制,嵌入式视觉,ADAS,算法加速,云计算,有线/无线通信等应用领域做原型开发。

/4

/4

curton 2019-10-11 22:37