先说一下这本书的情况吧,毕竟是个试读报告。

书全名叫运算放大器参数解析与LTspice应用仿真,由于作者就职于ADI公司,所以这本书的主要内容和ADI的产品(器件和软件)息息相关。从书名就能大概猜出本书的大致内容,运放参数解析和LTspice仿真,再看一眼此书的后封面,目录内容也是按这个来排列的。

二、重点内容 1. 输入失调电压(Input Offset voltage):

在室温25℃及标准电源电压下,输入电压为0时,为使输出电压为0,在输入端加的补偿电压叫做失调电压(Offset voltage, Vos)。作者在书中写了“短”:放大器输入两端电压相等,也提到 “虚”是引起输入失调电压的原因。

失调电压的案例分析里面的现象非常有参考价值,做为一名硬件工程师,对一些异常现象的原因分析是处理电路异常的重要环节,这个会对以后的电路调试有非常大的参考价值。

失调电压的定义和产生原因可以作为了解,我觉得对于应用来说了解即可。

失调电压的漂移定义需要认真了解一下,从硬件层面来说,温度和长期工作时间影响都是硬件电路设计必需要考虑的东西。

失调电压的测试于仿真都是对于设计方案的一种验证,是需要好好学习的东西。

失调电压的处理方法则是在设计中从应用层面对成本和外部条件的综合考量,需要认真解的部分,了解深入的好处是在设计中较易找到一个比较合理的平衡点。

2. 偏置电流(Input Bias Current)与失调电流(Input Offset Current)这是与“虚断”相关的参数。

输入偏置电流Ib :定义为流过两个输入端电流的平均值。

输入失调电压IOS :定义为流过两个输入端的电流之差。

输入失调电流和偏置电流所导致的直流噪声,是Ib+、Ib- 分别流入运放的同相和反相输入端的电阻网络所形成的电压差。

偏置电流案例分析中,案例很简单,但是确实是一个经常会忽略的问题。

偏置电流产生的原因是为了保障放大器内部晶体管工作在线性区,失调电流的产生原因就和失调电压相同了。

偏置电流的处理方法里面列出4中情况的正确处理偏置电流的方法都比较实用。

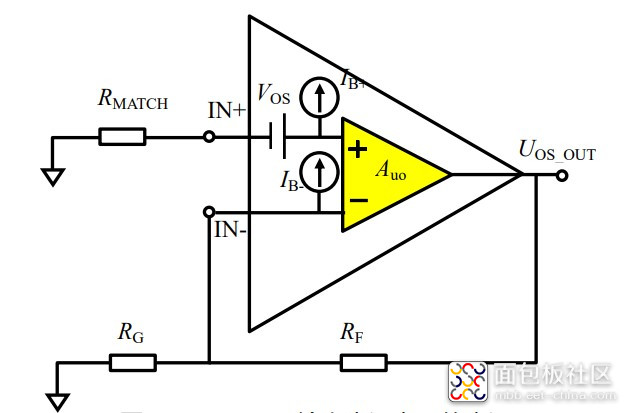

运放的输出失调电压是由输入失调电压,两个输入端的偏置电流和失调电流的总影响产生。

所以,决定输出失调电压大小的因素有:独立的输入失调电压,以及相互关联的偏置电流和失调电流,且后两个因素和外部电阻相关。

3. 共模抑制比(Common Mode Rejection Ratio, CMRR)这里面包含两个概念:

差模增益Ad :加载于两个输入端的之间的信号所获得的增益

共模增益Ac :同时加载于两个输入端的信号所获得的增益

共模抑制比定义为差模增益与共模增益的比值,即

共模抑制比的案例分析非常有意思,电路我也在网上找到了,贴出来看一下

|

ADA4522-2组建的差动电路 |

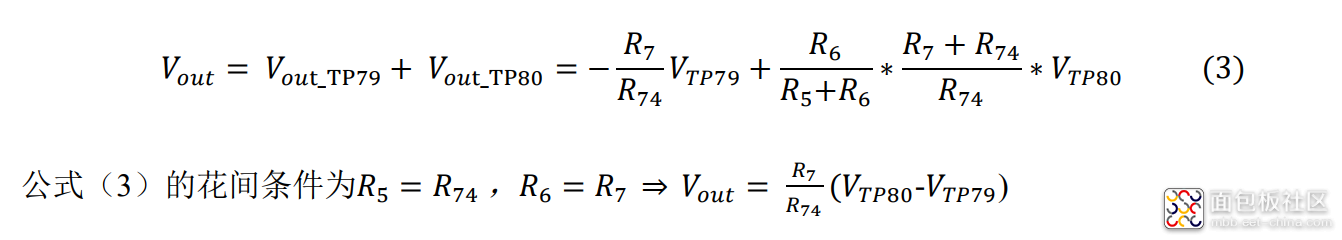

案例情况:使用2片ADA4522-2组建差动电路,第一级电路U8A、U8B实现差动电路的输入缓冲器功能,第二级电路U5A实现差动信号放大电路,其中,R6、R7阻值为30KΩ,误差为1%,R5、R74阻值为3KΩ,误差为1%,电路预期的增益设计为10倍。

核心客户在25℃恒温环境下使用设备,测试点TP76、TP77对地的共模电压为7V,在TP76、TP77之间输入26.5mV差模信号时,电路输出(U5A 1脚)为259mV,接近电路预期设计,但是当TP76、TP77输入差模信号为1mV时,电路输出(U5A 1脚)只有5mV,误差过大。

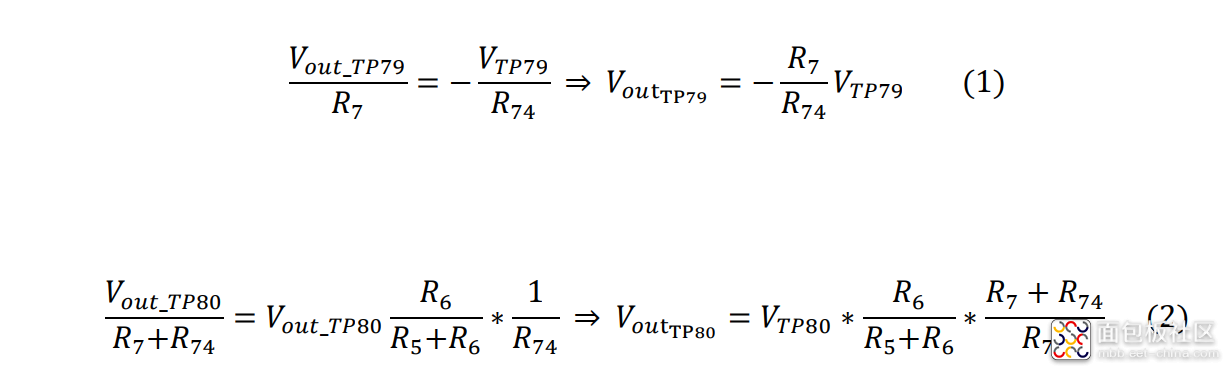

在这里,作者给出了电路分级测量定位故障的方法,具体操作有点复杂,我把这三个推导公式列出来作为参考,结果就不看了。

影响运放共模抑制比的因素有两个a.放大器输入级对称电路失配;b. 拖尾恒流源寄生电容随频率变化而变化。

电路共模抑制比与电阻误差,电路共模抑制比的影响因素有两个,一电路运放本身的共模抑制比,二是对称电路中各个电阻的一致性。如同书中所述,电阻误差将会放大运放电路本身的共模抑制比。

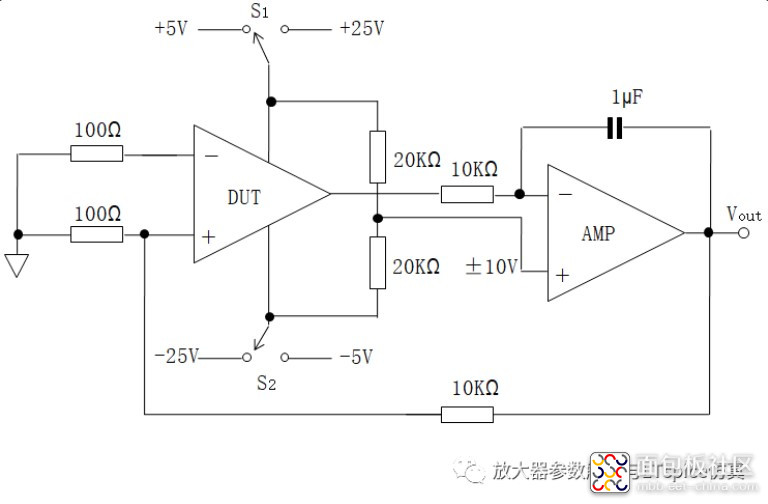

电路共模抑制比与信号源阻抗这里书中提到有效降低信号源内阻的方式是使用两个运放作为输入缓冲器来提高输入阻抗。电路图如下(电路来自作者公众号文章)

这部分先到这里,后面我再抽时间总结一下第四章的电源部分和第五章的仿真。

作者: 江湖独行, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3882390.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/5

/5

yzw92 2021-6-21 06:18