数字设计的核心器件是数字逻辑电路。而各种逻辑电路的核心是逻辑门电路。高速数字设计不可避免的要和逻辑门电路打交道,信号的反转,信号的质量,功率的需求等等都和逻辑门的高速特性有着密切的联系。这一章,我们主要研究高速信号下逻辑门电路所表现出来的特点,而重点集中在逻辑门电路的速度和功耗上。

1.MOS管和反相器[10]

1.1反相器

反相器是CMOS电路的核心。MOS管是构成反相器的基础。MOS管是一个四端口器件:b,s,d,g。

如果不打算深入研究CMOS电路的特性,那么,我们关注的最主要的是g,d,s,b的作用是第二位的,起着调节器件特性和参数的作用。从最基本的观点来看,可以把MOS看成一个开关,当加载GS的电压足够大的时候,SD之间形成导电层,有电流流过。MOS管部分可以参考[1]、[7]。

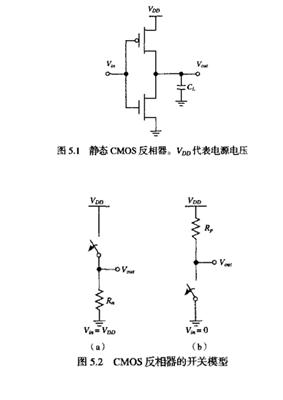

一个反相器可以由一个PMOS和一个NMOS构成,如图:一个反相器可以由一个PMOS和一个NMOS构成,如图:<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

当Vin为高的时候,NMOS导通而PMOS关闭,输出为低电平;当Vin为低的时候,NMOS关闭和PMOS导通,在Vdd和Vout之间形成一条通路,输出为高电平。

输出的高低电平分别为VDD和GND,因此电压摆幅等于电源电压。噪声容限很大。反相器的输入阻抗极大,因为输入是加在G级的,gate实际上是一个绝缘体,因此,稳态输入电流近乎为0。这就是为什么说理论上单个反相器可以驱动无穷多个门。一个反相器驱动一个负载时的示意图:

负载CL是接收电路的输入电容。我们来看一下这个电容由什么构成。

首先,对于驱动电路而言,在G和D之间存在一个电容Cgd,BD之间存在扩散电容Gsd,驱动下级电路的扇出电容Cg,以及互联的电容Cw。模型是:

1.2 CMOS的输出阻抗[10]

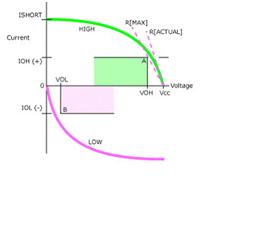

首先看一下CMOS电路的输出VI曲线。横轴是输出电压,纵轴是输出电流。

Figure 1: The V-I curve for a driver defines its behavior at all voltages.

这个图中有两条曲线。绿色表示的是输出转换到高的时候电压和电流的关系,紫色表示的是输出转换到低的时候电压和电流的关系。注意,这个曲线是静态曲线!也就是说,将输出接到一个负载上,然后负载慢慢的吸收电流;同理,转换到低的时候负载慢慢的释放电流。

CMOS电路的电压摆幅是0~VCC,也就是说,当输出为VCC时,驱动电流是0;当输出是0时,驱动电流是Ishort。这些都可以从图中看出来。当负载从驱动器拉出更大的电流时,在曲线上就向左移动。在横轴VCC附近,V-I曲线的斜率定义为驱动器的输出阻抗—— R[ACTUAL]。

器件的Datasheet通常指定一个VOH和IOH,我们都知道VOH-IOH表示了驱动器输出为高的时候的输出电流。

很明显,这指出了在保证输出为高的情况下(满足电压容限),能够从驱动器获得的最大电流(VoL-IOL的意义同理)。

那么,驱动器的最大输出阻抗是多少呢?

输出为高的时候,最大的输出阻抗: R[MAX] = (VCC–VOH) / IOH。

输出为低的时候,最大的输出阻抗: R[MAX]= –(VOL / IOL).

1.3信号标准和逻辑门系列

驱动器:驱动器从本质上看有两种模式——push-pull, current-steering。

推拉输出比较简单,直接设置电平,接收器判决电平然后接收;电流模式驱动器设置电流,然后通过端接电阻将电流转换为电压模式。推拉模式简单,功耗低;电流模式的信号质量好。由图可见,大部分差分电路都是电流模式的。

电流模式通过获得稳定的电流从而减小了噪声,因为dI/dt 很小。

/4

/4

文章评论(0条评论)

登录后参与讨论