作者:Arteris IP 首席技术官 (CTO) Benoit de Lescure

早在 1984 年,Sun Microsystems 公司的 John Gage 就提出了“网络即计算机”的理念。事实证明,这一观点很有远见。如今,这种理念再次兴起,而这一次涉及的是片上系统 (SoC)。芯片上不同功能之间不是通过简单的导线相互通信,而是通过复杂的网络元素(例如交换机、协议转换器、打包器等),这与 1984 年计算机组通过机柜或房间中的网络进行通信没有太大区别。

在 SoC 出现之前,工程师通过导线在电路板的不同元件间传输数据。这种方法最大的困扰在于导线长度管理以及如何确保不同元件使用完全相同的协议进行通信,但也仅此而已。实际操作在计算元件中进行。然后,在这些珍贵元件之间布线就是简单的设计工作了。

随着 SoC 功能扩展,将整个电路板甚至更大的系统整合到单个芯片上变得可行,所有这些电路板和系统都由中央处理器 (CPU) 或处理器集群控制。每个 CPU 都运行软件来协调系统处理需要通过软件提供灵活支持的功能。在这种情况下,处理器提供商(如 Arm 公司等)的解决方案得以迅速发展。其他供应商也紧随其后,包括除 CPU 以外的其他功能的知识产权 (IP) 提供商。起初是通过提供外设 IP 处理许多接口协议,然后逐渐发展为采用专用于无线通信、图形处理、音频、计算机视觉和人工智能的处理器完成。除此之外,还可以采用片上工作存储器、缓存存储器、双数据速率(DDR) 接口以及芯片外/裸片外 DRAM 等等。

高级 SoC 中可以集成许多不错的功能,但这些功能要如何通信?不能采用直接连接的方式,因为整个芯片将被导线覆盖,并且这种方式会降低CPU 和存储器确定下一步操作的速度。更好的做法是所有流量都通过高速通道进行路由,并在流量进入高速通道前进行管控。如果 IP 想要与 CPU 通信,必须排队进入高速通道(反之亦然)。

总线不再是普通的导线。总线逻辑会监测谁正在进入高速通道、允许谁下一个进入高速通道,并且安排支持的数据在以不同速度运行的域之间有序流动。流水线寄存器有助于跨越很长的距离,同时满足时序限制的要求。许多集成团队将其称为“总线结构”,即通过控制逻辑、多路复用、寄存器和先入先出的队列组织连接。

有了总线结构架构后,就可以构想不同用途的架构了。仅 AMBA 系列就有多种类型,每种类型都有自身的优势和限制。而复杂的 SoC 很可能需要采用其中的几种类型。但是,还有另一种截然不同的技术,即片上网络 (NoC),其概念完全不同,并且不会将互联通信与物理传输紧密耦合,因此提供了新的架构方案。我将在下一篇博客中对这些方案的相对优势进行详细讨论。

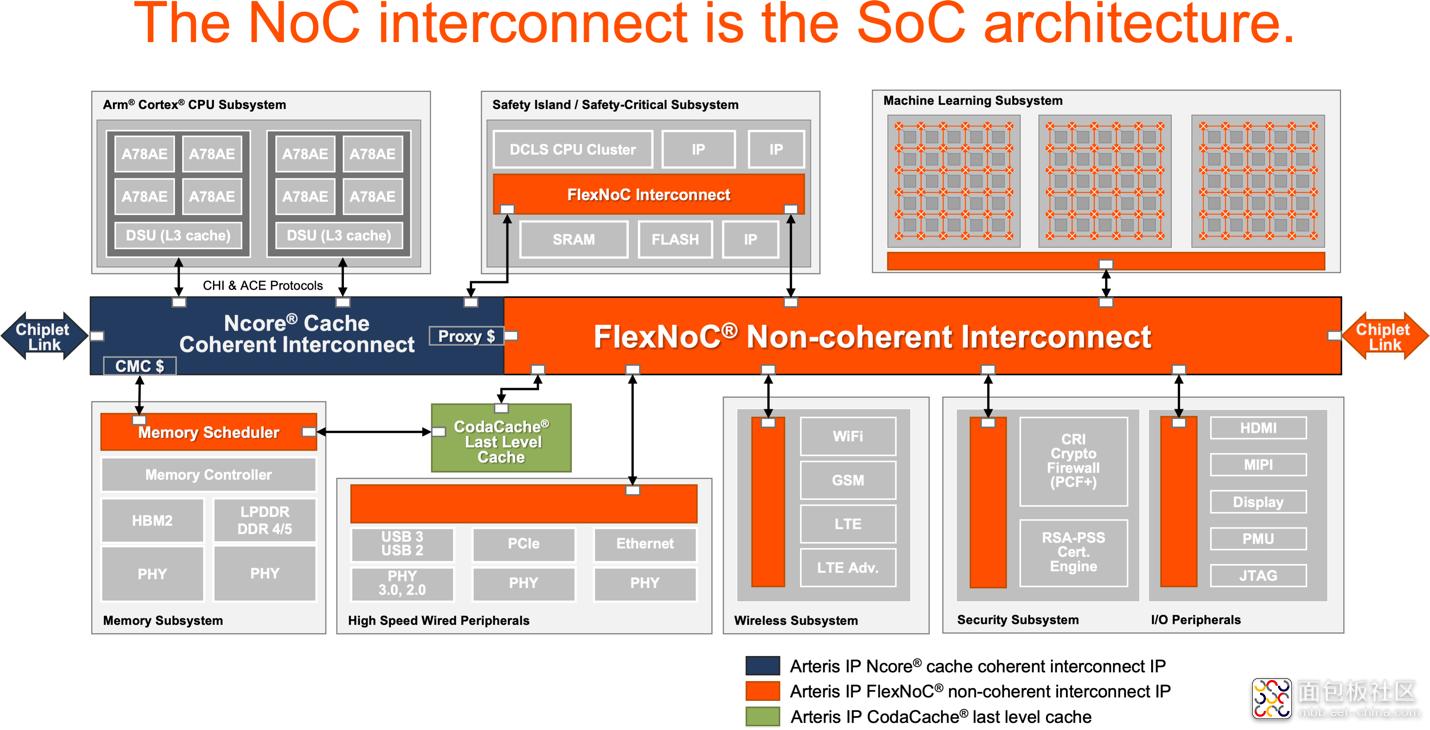

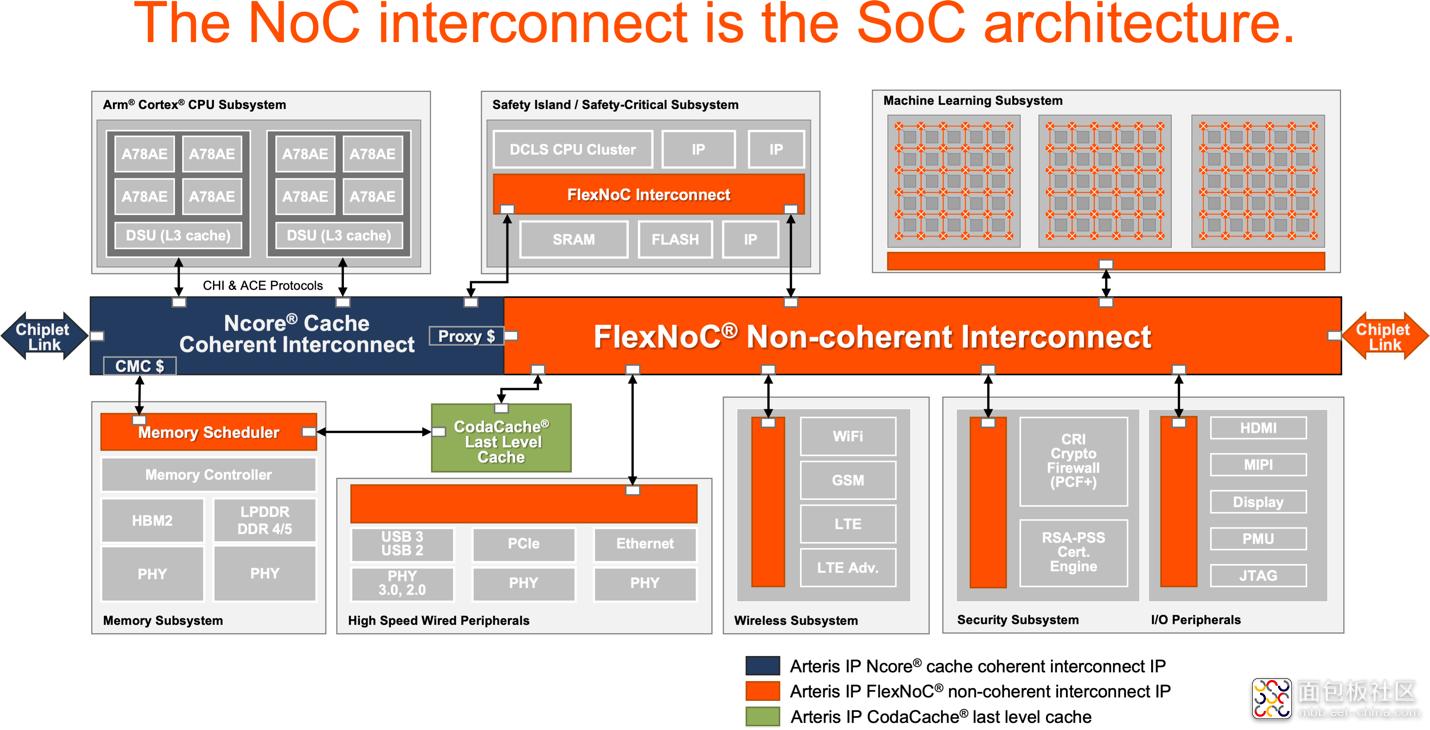

此外,还存在另一个重要的考虑因素。目前,典型 SoC 的构建将基于许多第三方 IP 和一些集成商自有 IP,从而获得定制优势。但是优势有多大呢?竞争对手可以购买相同 的第三方产品,从而削弱可能获得的竞争优势。这样一来,挑战就变成了设计团队如何有效地集成其 SoC。好消息是,针对这种高效集成的需求,我们确实有文章可做。带宽、吞吐量、服务质量、功率、安全性和成本都取决于集成程度。这些因素受已实施通信架构(很可能是 NoC)的影响,下一篇博客将对此进行讨论。最终,提高芯片竞争力的关键因素在于精心选择的 IP 和片上通信体系架构。NoC 已成为 SoC。

下一篇:为什么 NoC 大规模取代了Crossbar 互联

作者: Benoit, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3957553.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/1

/1

文章评论(0条评论)

登录后参与讨论