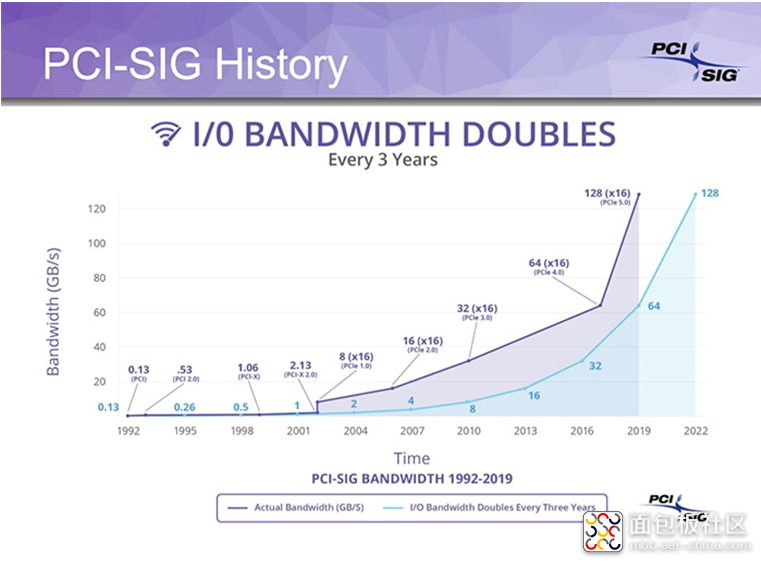

随着PCI Express标准从第4代 (16.0 GT/s) 进化到第5代 (32.0 GT/s),其信号速率从PCIe 4.0的16GT/s提升到了32GT/s,PCIE 5.0依然使用128/130编码方式,x16带宽从64GB/s提升到了128GB/s。

经过2010~2017年间的沉寂后,PCI SIG正加速其发展蓝图(来源:PCI SIG)

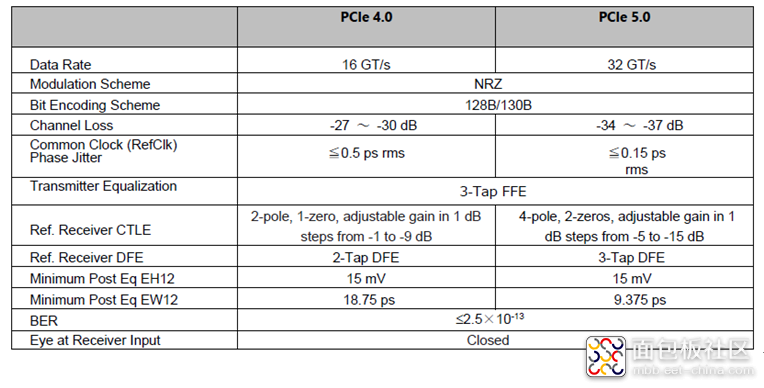

PCIe 4.0和5.0的异同

除了带宽翻倍之外,PCIe 5.0还带来了其他变化,例如改变电气设计以改善信号完整性,向后兼容PCIe等等。此外,PCIe 5.0还设计了新标准,减少延迟,并降低长距离传输中的信号衰减。

PCIe 4.0和5.0具备许多共同点:两者均使用 NRZ 调变、128B/130B 编码,相同的 2.5×10-13 BER 目标以及相同的连接器脚位排列。发射器使用相同的 FFE 方式,并具有 11 组接头预设 (P0-P10)。

相较于PCIe 4.0使用的2-pole、1-zero CTLE响应,PCIe 5.0使用4-pole、2-zero CTLE 滤波器响应。新的 CTLE 提供更大的弹性,以及从-5到-15 dB更深的增益范围。PCIe 5.0还增加了第三个参考接收器(DFE)。

速率从16GT/s提升到32GT/s的最大困难,莫过于最大允许损耗从30dB增加到37dB;毫不意外的是,PCIe 5.0通道要求也一并历经了重新定义,因此板卡机电 (CEM) 规格要求扩充卡只能采用表面黏着贴装连接器。工程师也因为资料速率加倍而面对各种新的验证挑战:

1. 克服更高的通道损耗及符号间干扰

2. 设计能在更加受限的环境中,以较小边际运作的组件及平台

3. 同时在物理层和通讯协议层进行除错

发送、接收端测试规范

发送端的测项包含:

1. Tx Signal Quality Test

2. Tx Preset Test

3. Tx LEQ Test

4. Tx Initial TXEQ Test

5. Lane Margining Test

6. PLL Test

7. CLK Test

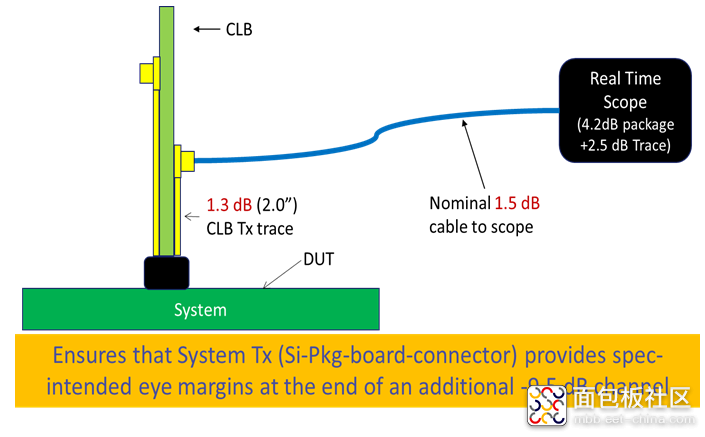

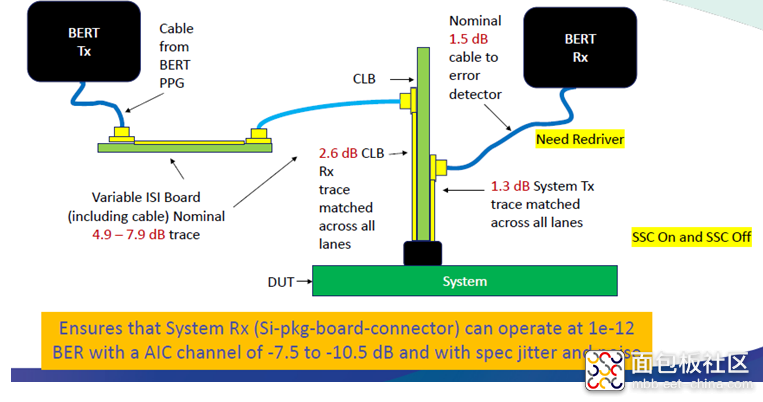

*System Tx Diagrams*

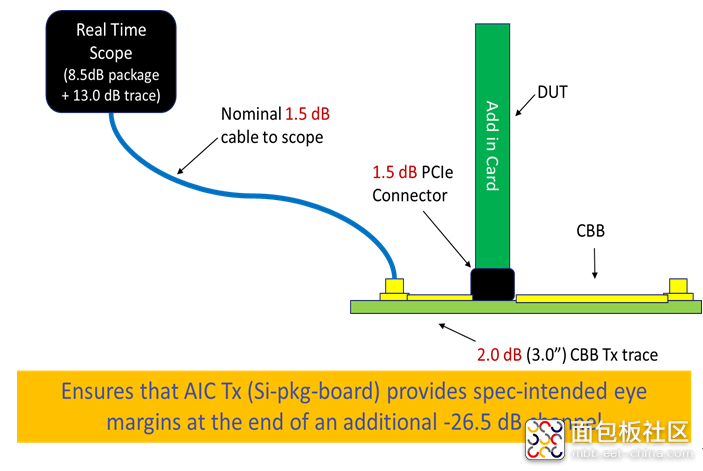

*AIC Tx Diagrams*

接收端的测项包含:

1. RX BERT Test

2. RX LEQ Test

作者: 百佳泰测试实验室, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-400317.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/5

/5

夜兮 2021-5-14 10:03