原创

ameya360分享:放心交给AI解决的芯片设计痛点

2022-11-8 09:55

746

4

4

分类:

机器人/ AI

尽管制造工艺的推进速度已经放缓,芯片设计的复杂程度依然丝毫不减,对于芯片设计者来说,在这样一个AI驱动的时代下,如果不能将AI为自己所用,无疑会让自己乃至整个设计项目的效率停滞不前。虽说大家都已经察觉到AI开始渗透进EDA工具中,那么现阶段的AI,究竟能解决哪些设计上的挑战呢?

验证是芯片设计中最大的挑战之一,我们已经见识过了价格高昂的专用验证硬件,以及验证上云的潮流,这些都足以说明验证是芯片设计中一个多么耗费资源的过程,这里指代的也不仅仅是硬件计算资源,还有时间资源。验证所耗时间甚至可能高过其他流程,这些年诸多芯片开发团队中的验证工程师人数也在逐渐增长,增速甚至已经超过了设计工程师,然而业内却很少有人去优化验证这个流程。

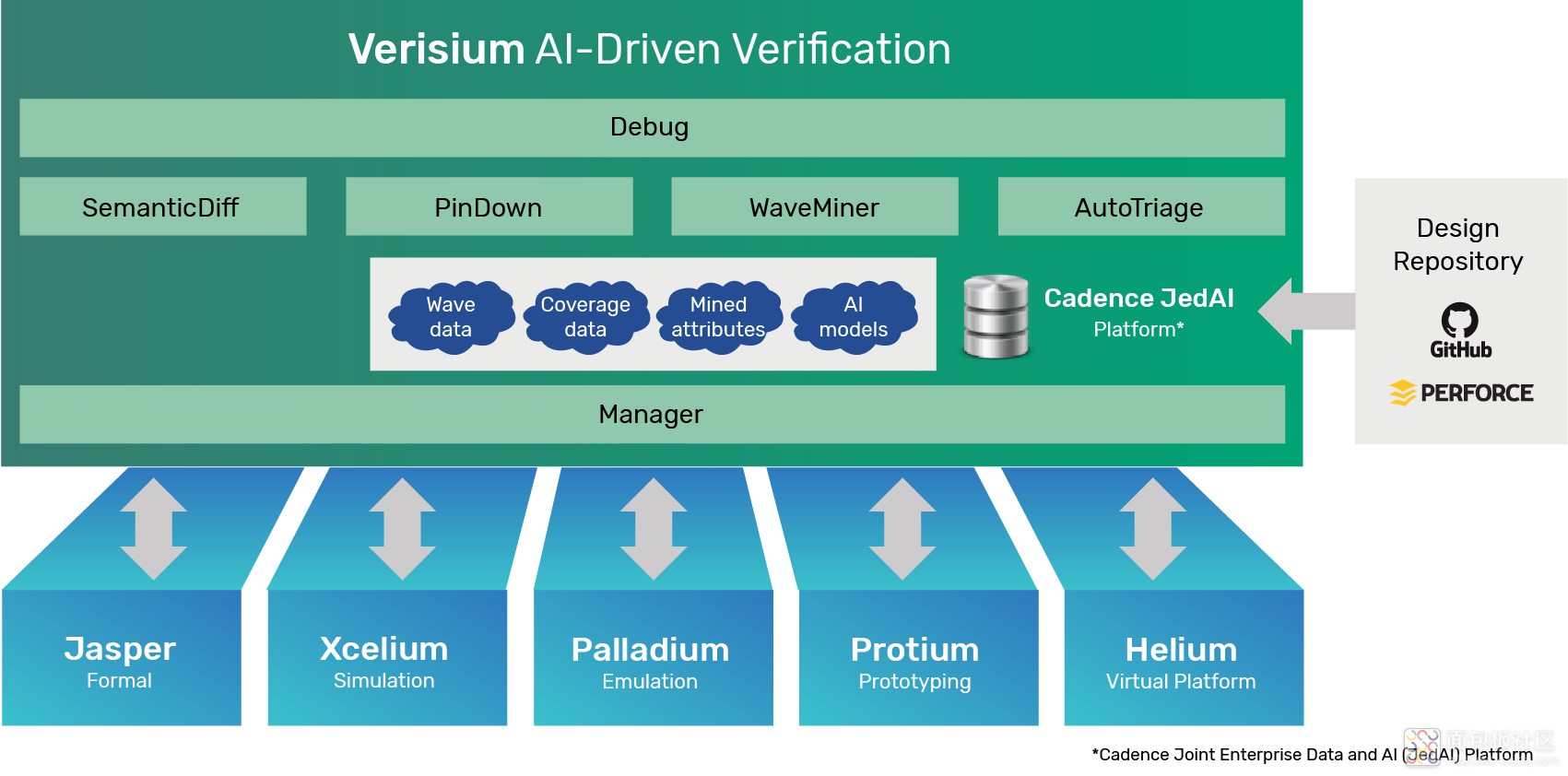

AI的出现终于让这个缺口出现了松动,不少厂商都开始利用AI去优化验证这一流程,比如通过覆盖率预测和激励优化来加速覆盖率达标。Cadence也在今年发布了Verisium AI驱动验证平台,根据Cadence的说法,Verisium的出现意味着SoC验证从单运行单引擎算法,转向了由AI和大数据辅助的多运行多引擎算法,从而减少了调试周转时间、提高了调试效率,还会自动对失败测试案例分类,减少人为分析的工作量。

相对数字IC设计来说,模拟IC的设计显然在自动化程度上还是差了不少的。在数字电路的设计过程中,整个流程的自由度是在逐级降低的。模拟电路设计虽然也是如此,但其下降幅度还是不比数字电路设计的,尤其是在布局布线和验证上,所以自动化一直没有提上日程,现阶段大部分模拟电路设计主要还是取决于设计者本身的直觉、技能和经验。

有了AI的帮助后,EDA工具在大量数据的训练下给出了先进的机器学习算法,使得模拟电路的布局布线有了更高效的自动化流程,尤其是在约束提取和生成,布局优化上,模拟电路的优化和生成及仿真验证也可以在AI驱动下获得提速。如此一来,每个模拟电路设计的迭代数量会进一步减少,芯片的上市周期也随之缩短。

近几年流行起来的UCIe、Chiplet、3D封装等,其实都是一个系统集成的概念。以此引入的设计与制造优化方案也受到了持续关注,比如DTCO等。如何集成更多的晶体管、更多的内存以及逻辑+内存集成,还有最后软件联合硬件的热管理等,都是系统集成需要考虑的问题。

/4

/4

文章评论(0条评论)

登录后参与讨论