可一到运行起来就蛋疼了,呵呵….

下面分析一下,仅供参考,若有不对,敬请指正!

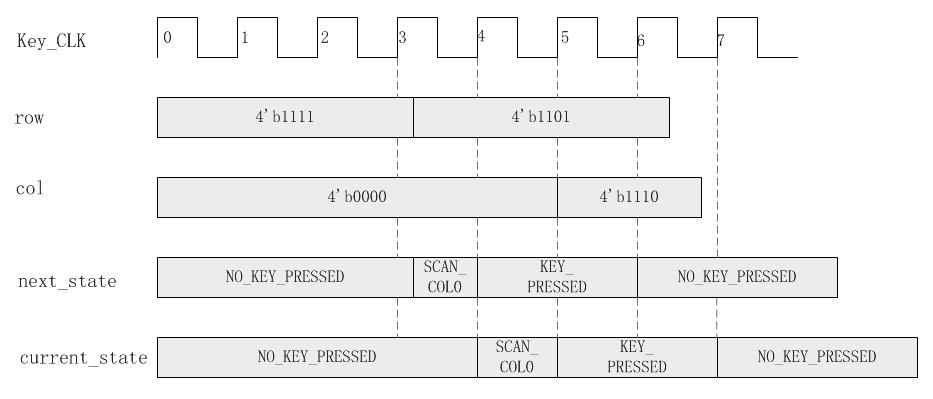

看上面时序图在

1、第0~2个时钟周期内

row(输入)为4’b1111代表无键按下,next_state=NO_KEY_PRESSED,Current_state= NO_KEY_PRESSED无限循环….

2、在3个时钟周期内

第3个上升沿之后(注意是“之后”),假设第1列、第1行的键按下,此时row=’4b1101, next_state=SCAN_COL0, urren_state=NO_KEY_PRESSED; col=4’b0000 ;

3、在4个上升沿时

因为col=4’b0000; row=4’b1101 ;所以next_state=KEY_PRESSED ;

此时current_state = SCAN_COL0 。

4、在第5个上升沿时

Curren_state=SCAN_COL0生效,即col=4’b1110 ;

同时current_state=KEY_PRESSED 。

5、第6个上升沿

因为col=4’1110 , row=4’b1101 ,(前面说过是第1列、第1行的键按下),所以row==4’hF, next_state=NO_KEY_PRESSED;

同时current_state=KEY_PRESSED生效,装载值col_val=4’b1110, row_val=4’b1101;很显然这个值不对,(正确的应该是col_val=4’b1101, row_val=4’b1101)。

大家有没有发现到第6个上升沿的时候,本来next_state应该要跳转到SCAN_COL1但是现在是跳转到NO_KEY_PRESSED,也就是说SCAN_COL1状态被跳过了,状态只能在NO_KEY_PRESSED和SCAN_COL0之间切换。

经过分析发现,是Col值的变化延迟导致的,换句话说,如果col的变化能在下一次判断nex_state(第4个上升沿)之前及时变化的话,状态的判断就不会出错。

/2

/2

文章评论(0条评论)

登录后参与讨论