多核异构系统是⼀种使同⼀颗SoC芯片中不同核心分别独立运行不同平台的计算系统。通过合理的处理器核心及外设资源划分,使⼀颗SoC芯片能够独立运行Linux系统和实时性系统,在满足系统软件功能和硬件外设丰富性要求的同时,也满足系统的实时性要求,具有突出的性价比优势和产品体积优势。

“瑞芯微多核异构系统”是瑞芯微提供的⼀套通用多核异构系统解决方案。

在运行平台方面:

Linux提供标准的Linux Kernel,RTOS提供开源的RT-Thread ,Bare-metal提供基于RK HAL硬件抽象层的裸机开发库。同时,瑞芯微多核异构系统支持客户自行适配更多的运行平台,例如可以基于RK HAL硬件抽象层适配指定的RTOS等。

在处理器核心方面:

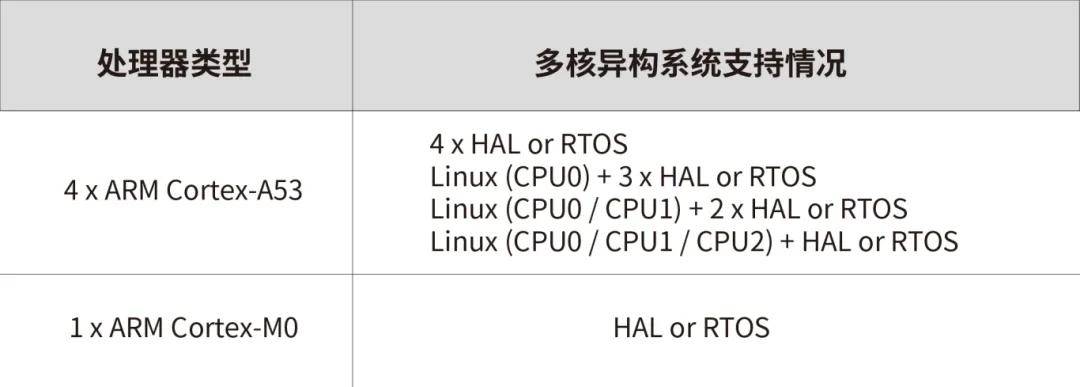

瑞芯微多核异构系统支持SoC中同构的ARM Cortex-A核心独立运行。也支持SoC中异构的ARM Cortex-M或RISC-V核心独立运行。瑞芯微多核异构系统通过合理的处理器核心资源划分,将适当的任务分配到最适合的核心进行处理,从而使SoC发挥出更优秀的性能和能效表现。

目前,瑞芯微多核异构系统采用无监督的AMP方案。不使用虚拟化管理,从而在运行实时性系统时获得更快的中断响应,以满足电力、工控等行业应用中严苛的硬实时性要求。

处理器核心

AMP支持情况

中断嵌套是一种有效的中断处理机制,它允许系统根据中断的优先级来响应和处理中断,从而确保关键任务能够及时得到处理,具有实时性高、灵活性好、响应快速等特点,但传统的Linux系统为了简化设计、提高系统的稳定性和可预测性、减少资源竞争和死锁等风险、以及提高兼容性和可维护性,不支持中断嵌套。这种设计选择使得Linux内核在许多应用场景中表现出色,但对于高实时性场景下的应用就显得力不从心了。

开发板型号:OK3562J-C

资料版本:OK3562-C_Linux 5.10.198_用户资料_R1

测试思路:

使用两个GPIO,分别为GPIO4B1和GPIO0B0,其中GPIO4B1设置为输出,GPIO设置为输入并且中断配置为下降沿触发。硬件上短接GPIO4B1和GPIO0B0。使用Timer4定时器每秒产生一个定时器中断,在中断处理函数中控制GPIO4B1产生一个下降沿并延时,如果出现了GPIO0B0中断处理函数中的打印信息则证明成功发生了中断抢占。

测试步骤:

(1)编写测试程序fltest_irq_preempt.c开启TIEMR4和GPIO0B0的中断并且将GPIO0B0配置为下降沿触发,在定时器中断处理函数中将GPIO4B1拉高拉低,使之触发GPIO0B0的中断,在GPIO0B0的中断处理函数中打印一句话来表明当前进入了GPIO0B0的中断;

(2)修改中断路由,添加TIMER4和GPIO0的中断并使之绑定给CPU3,并设置TIMER4的中断优先级高于GPIO0;

(3)重新编译镜像并烧写;

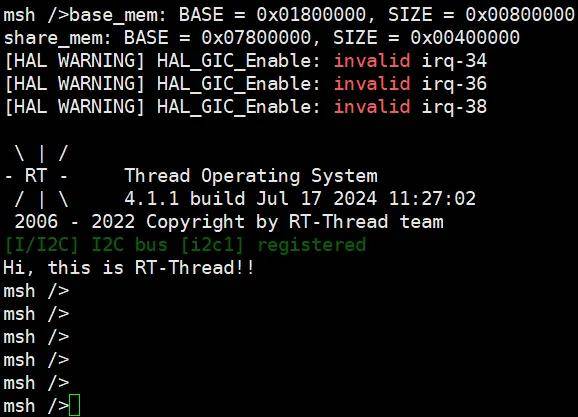

(4)在uboot菜单中打开AMP并重启OK3562J-C开发板,此时RTOS调试串口打印如下:

按tab键可以打印出当前的所有命令:

可以看到我们的命令已经注册成功了。

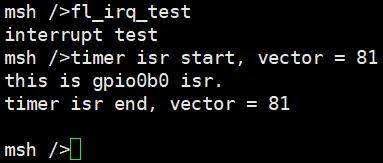

现在执行我们刚刚编写的fl_irq_test这条命令,即可看到效果:

可以看到GPIO0B0的中断抢占了当前的TIMER4中断。

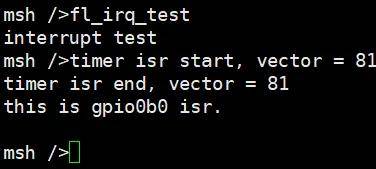

我们将二者的优先级调换一下再重新编译烧写,然后再次执行该程序,可以看到GPIO0B0的中断在TIMER4中断结束之后才被处理,未发生抢占。

作者: 飞凌嵌入式, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-4034253.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/5

/5

文章评论(0条评论)

登录后参与讨论