简单介绍一下我学习如何使用quartus ii进行波形仿真,作为以后使用,下面是计数器的vhdl代码

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity cnt4 is

port

(clk:in std_logic;

rst:in std_logic;

en:in std_logic;

outy: out std_logic_vector(3 downto 0);

cout: out std_logic

);

end ;

architecture timer of cnt4 is

signal tmp : std_logic_vector(3 downto 0);

begin

process(clk,rst,en)

begin

if(rst='1')then

tmp <="0000";

elsif(clk'event and clk='1')then

if en ='1' then

tmp<= tmp+1;

end if;

end if;

outy <= tmp;

end process;

cout <=tmp(0) and tmp(1) and tmp(2) and tmp(3);

end ;

使用quartus ii建立工程我就不叙述了,只介绍如何仿真

当编译通过后

0.

新建:选择vector Waveform File,出现如下界面

1.

点击保存,出现一个另存为的对话框,已经有一个默认的文件名了(会和你的工程名一样的,默认后缀名是.vwf),直接点击保存即可。

2.

点击edit菜单下的End time,在出来的对话框中的time中输入50 ,后面选择us,表示视图中表示50us的大小

3.

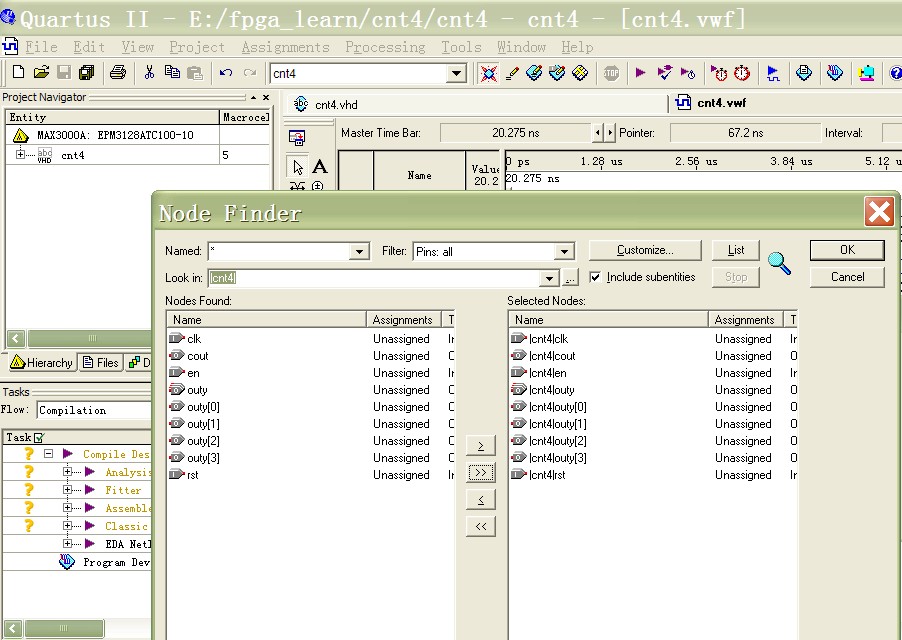

点击edit菜单下的insert 项的insert node or bus.. ,出来一个对话框,点击按钮“node Finder”,出来一个对话框,在Filter中选

择Pins:all,点击后面的按钮“List”,然后会左边框中会出来一系列和程序相关的输入输出节点:有4个选项:

>= : 选一个,>>表示全选;<=删除一个,<<,全删

点击>>之后,右边框中都出现了所有的发现节点(对此例子会出来5个大节点参数,如下图),

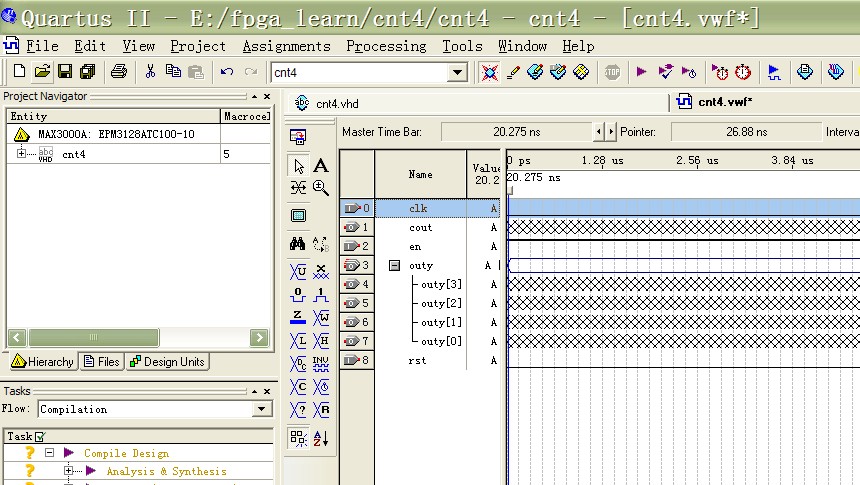

之后点击ok,ok,之后会出现如下图所示:

4.

点击住clk行,然后再点击左边的工具框中的overwrite clock(你可以把鼠标放在上面,它会显示出来的),在time period选项下的

period中输入1,后面选择us,表示周期,后面的duty cycle中不用修改(默认的是50),表示占空比。

5.

点击住en行,然后再点击左边的工具框中的forcing high(标示为一个1下面一个波形符号的),赋值为1

6.

点击住rst行,然后再点击左边的工具框中的forcing low(标示为一个0下面一个波形符号的),赋值为0

7.

设置完成。

点击start simulation,出来一个对话框,点击是。

8

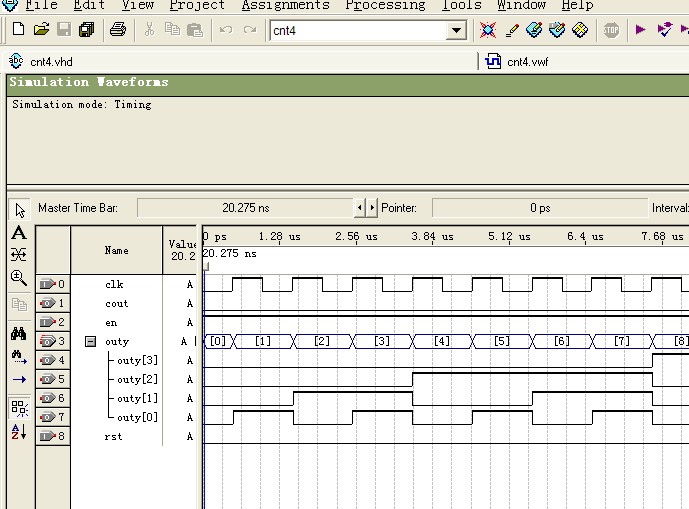

完成后,会出来一个succss,并且会出来仿真后的波形,如下,会发现,计数器仿真正确

/5

/5

用户413306 2012-2-3 21:29