[初次发表 24-05-01 最后编辑:24-08-01]

MOSFET也叫MOS,它是一种三端子器件,包含两个PN结。

MOSFET的微观结构主要分为2类——平面结构(Planar)和垂直结构(Vertical)。

1. 平面结构 Planar

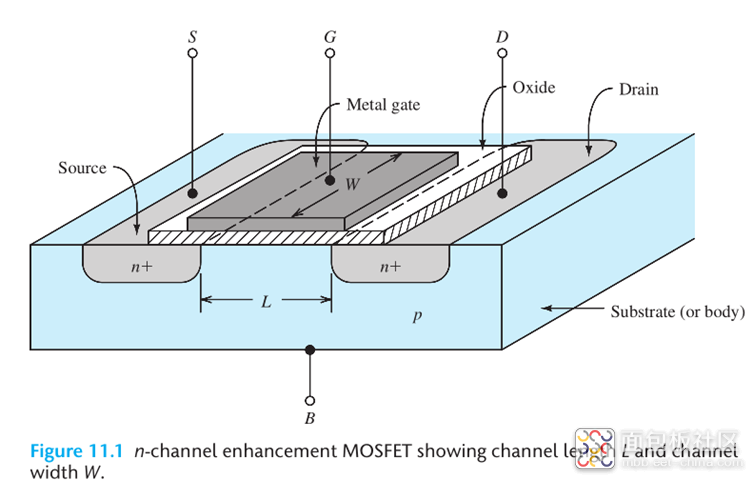

平面结构是指MOSFET的漏极电流方向平行于晶圆表面。结构示意图如下,分3层:顶层深色部分是栅极(G, Gate),使用高掺杂的多晶硅或铝制造;栅极下面的白色薄片区域是栅极氧化层(Gate Oxide),简称栅氧,用纯净的二氧化硅制造。这个部分是MOSFET的关键;栅氧两侧浅灰色区域是源极(S, Source)和漏极(D, Drain);最后是底部蓝色部分,这个是衬底(B, Body或Substrate),下图使用的是 p型掺杂衬底。硅的部分加工好了,最后要在G、D、S和B上制作低电阻的引出线。

从上图可以看出:

1. S极和D极可以互换。二者形状相同,掺杂浓度都是n型重掺杂(n+)。这和双极型晶体管的发射极、集电极不能互换是不一样的。

2. S极、D极和B极组成了一个NPN三极管(寄生三极管)。最好把B极和S极短接在一起,避免因B极悬空而使B-S结受到干扰。

图中S和D之间的距离L,定义为MOSFET的沟道长度,W定义为沟道宽度。L 的距离越小,平面型MOSFET的尺寸就越小,密度可以提高,所以也把 L 称为线宽。例如台积电/TSMC最新的2nm生产线,2nm就是指这个线宽。请注意,硅原子的直径是 0.117nm。当然,TSMC用了复杂的Fin-FET工艺来实现2nm,其微观结构不是上图这么简单。

下图是电镜下的平面型MOSFET表面,若干个MOSFET叉指状并联。

(图片来自PCIM 2000 Conf.,侵删)

CMOS器件和一些小信号MOSFET主要用平面型结构。对半导体晶圆加工过程(前道)有所了解之后就知道,平面型结构便于加工制造和等比例缩小。所以,制造CPU、存储器这两种典型的CMOS器件时选择平面型MOSFET,也产生了“摩尔定律”(Moore's Law)。

MOSFET及其沟道小型化的同时也带来了两个问题。

第一,D-S之间耐压(雪崩击穿电压)下降。要防止材料发生雪崩击穿,只有3个方法:降低电压差,增加线宽,降低掺杂浓度。CPU、存储器的厂家们在密度(利润)和耐压之间选择了降低电压差,所以集成电路的内核电压越来越低,从早期的5V,逐步降低到1.25V。

第二,载流能力受金属电极限制。金属电极常常是用沉积(Deposition)工艺制造的,是一层薄膜,限制了厚度。金属电极需要在MOSFET所在区域的顶层按S/G/D三个极性分别独立引出,各自的宽度也受限。根据电阻的计算公式可以知道,当MOSFET越做越小,电极电阻会越来越不可忽略。

不是所有的MOSFET都被用于制造CPU和存储器,还有功率MOSFET这个重要的门类啊。功率MOSFET D-S之间必须承受高压,500V以上是家常便饭。功率MOSFET需要控制大电流,1A~300A都有。增加线宽、使用金线可以降低电阻和功耗,但是也降低利润;降低掺杂浓度,发热大性能没法儿看,平面型MOSFET的问题让功率MOSFET进入了困境。

2. 垂直结构 Vertical

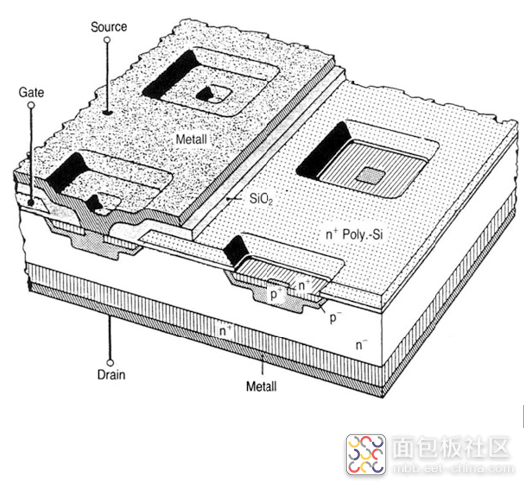

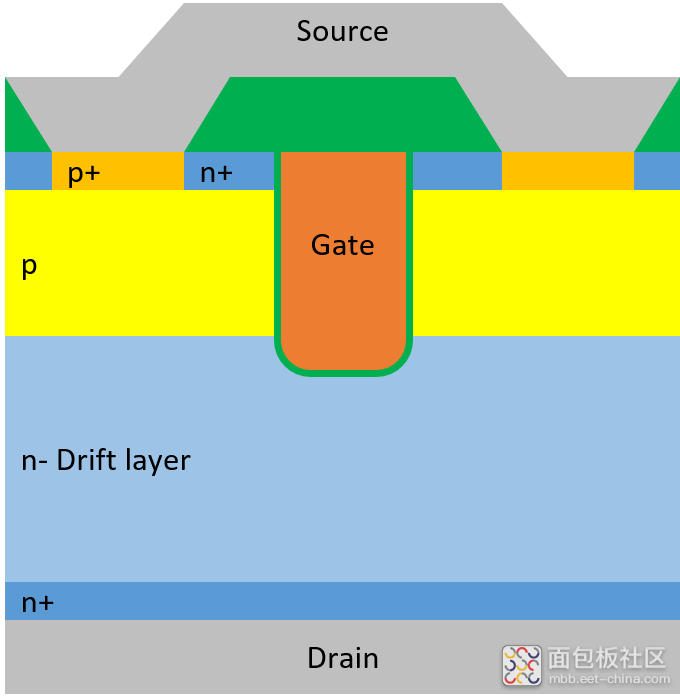

为消除平面结构MOSFET在处理高压、大电流时的局限,可以把D极移动到B极的下面,并在B极和D极之间加一个低浓度掺杂(n-)的外延层(Epitaxial Layer),形成一种D-S垂直结构。这样做可以利用外延层来确保D-S的耐压能力,而栅极沟道的工艺并不做改变。

(图片来自PCIM 2000 Conf.,侵删)

但是,又产生了新问题——外延层的掺杂浓度比衬底层还低,这意味着D-S导通时,外延层载流子密度低,等效电阻大,发热量大。

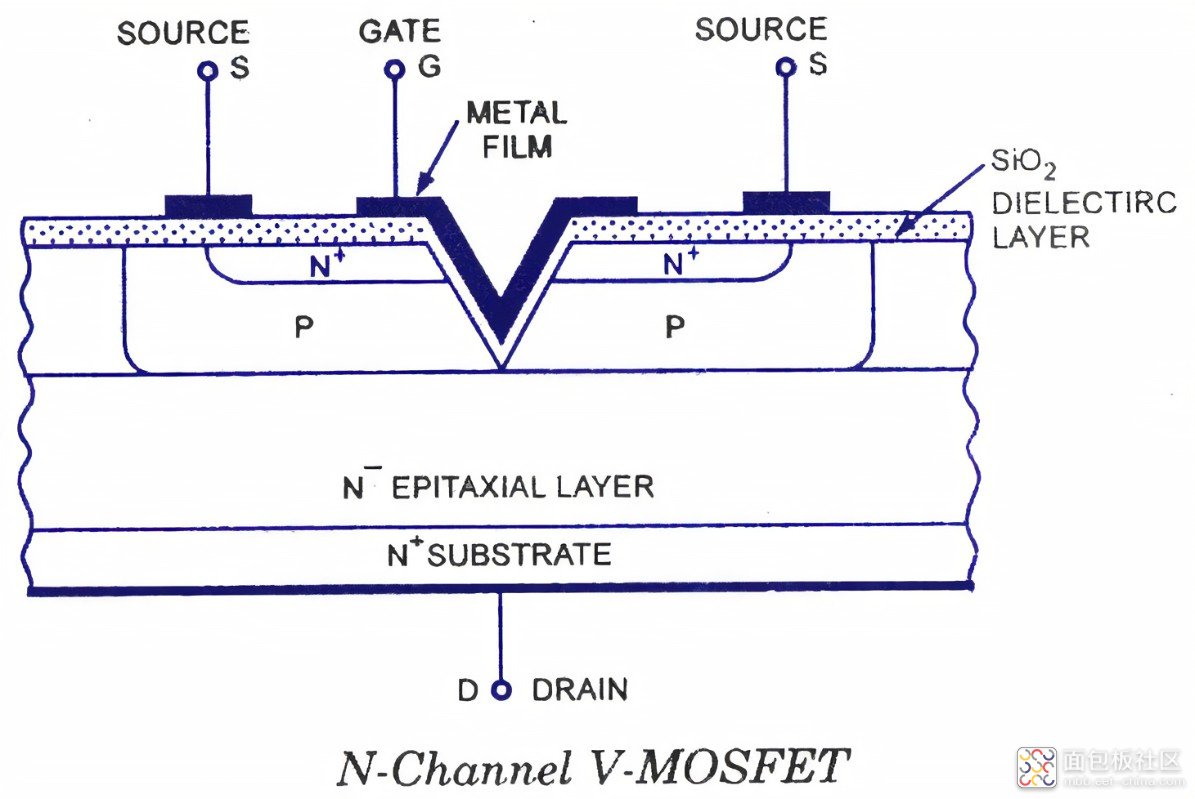

增大沟道的表面积可以降低电阻。电场强度定义为电场方向上一定面积内电力线的数量(面密度)。只要增大沟道的截面积,就可以在不改变衬底材料的情况下降低电场强度。至此人们开始在栅极的形状上下功夫:1970年代出现了 V形栅极(V-MOS),栅极向下深入衬底(下图);之后,有了栅极被栅氧完全包围的VD-MOS;1990年代推出了 U形栅极的U-MOS;接下来是沟槽栅技术(Trench),包括TMOS、RMOS和UMOS;从沟槽栅发展出了三个路径,分别是 Siliconix(现Vishay)的WFET 槽底厚栅氧结构,Fairchild(现Onsemi)的分离栅 PowerTrench,Infineon的CoolMOS超级结。

(图片来自网络,侵删)

(图片来自网络,侵删)

功率MOSFET器件普遍采用垂直结构。

Ref:

[美]Hambley.熊兰 等译.电工学原理与应用(第7版).电子工业出版社.2021

张波,罗小蓉,李肇基.功率半导体器件电场优化技术.电子科技大学出版社.2015

Josef Lutz.Semiconductor Power Devices.Springer.2010

/1

/1

文章评论(0条评论)

登录后参与讨论