原创

元器件第032篇 功率MOSFET 封装

2024-5-5 15:20

889

6

6

分类:

模拟

文集:

元器件

功率MOSFET的D极附近产生的热量最多。功率MOS采用垂直结构(另见元器件第029篇 MOSFET 结构 分类),由于低掺杂(高电阻率)的外延层位于D极附近,所以D极附近较内部其它部分会更热一些。也就是说,只要能把D极的热尽量带走,那么就抓住了这个问题的“牛鼻子”。为此,行业是怎么做的呢?

1. 背金(Back Metal)

一般的封装结构是把芯片颗粒(Chip,Die)用胶水粘在金属框架上(Frame),这个过程叫 Die Bonding,简称DB、固晶或粘晶。芯片产生的热量可以通过胶传导给金属框架,进一步传到到电路板。

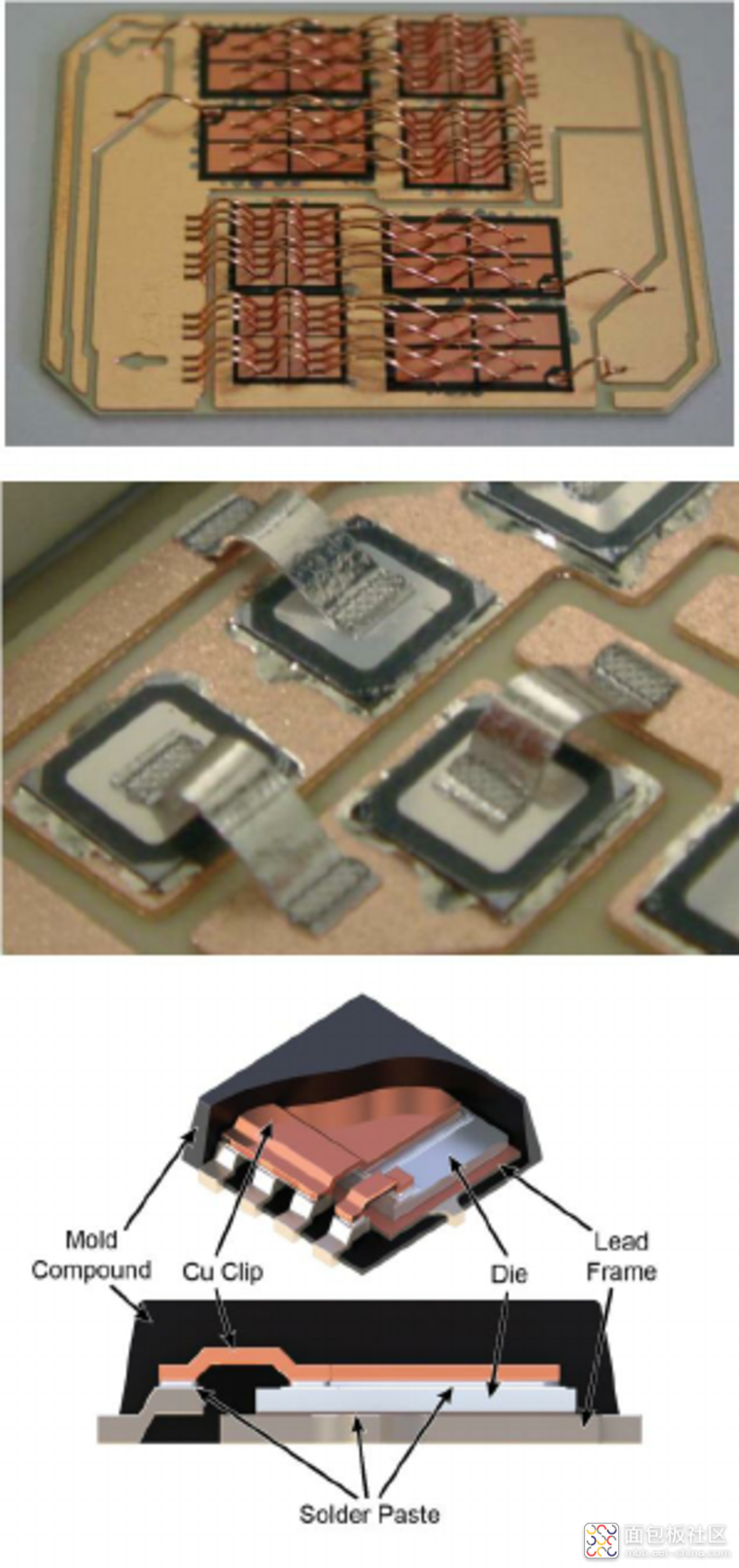

功率MOS通常在芯片背面加镀金属,这种做法叫背金。功率MOSFET的D极位于衬底下表面(背面),是一层金属膜,所以干脆把胶水换成锡膏,让芯片直接焊在金属框架上。有时不用锡膏而用铜钯金,这是一种和芯片的热膨胀系数更加匹配的材料。

2. 引线键合

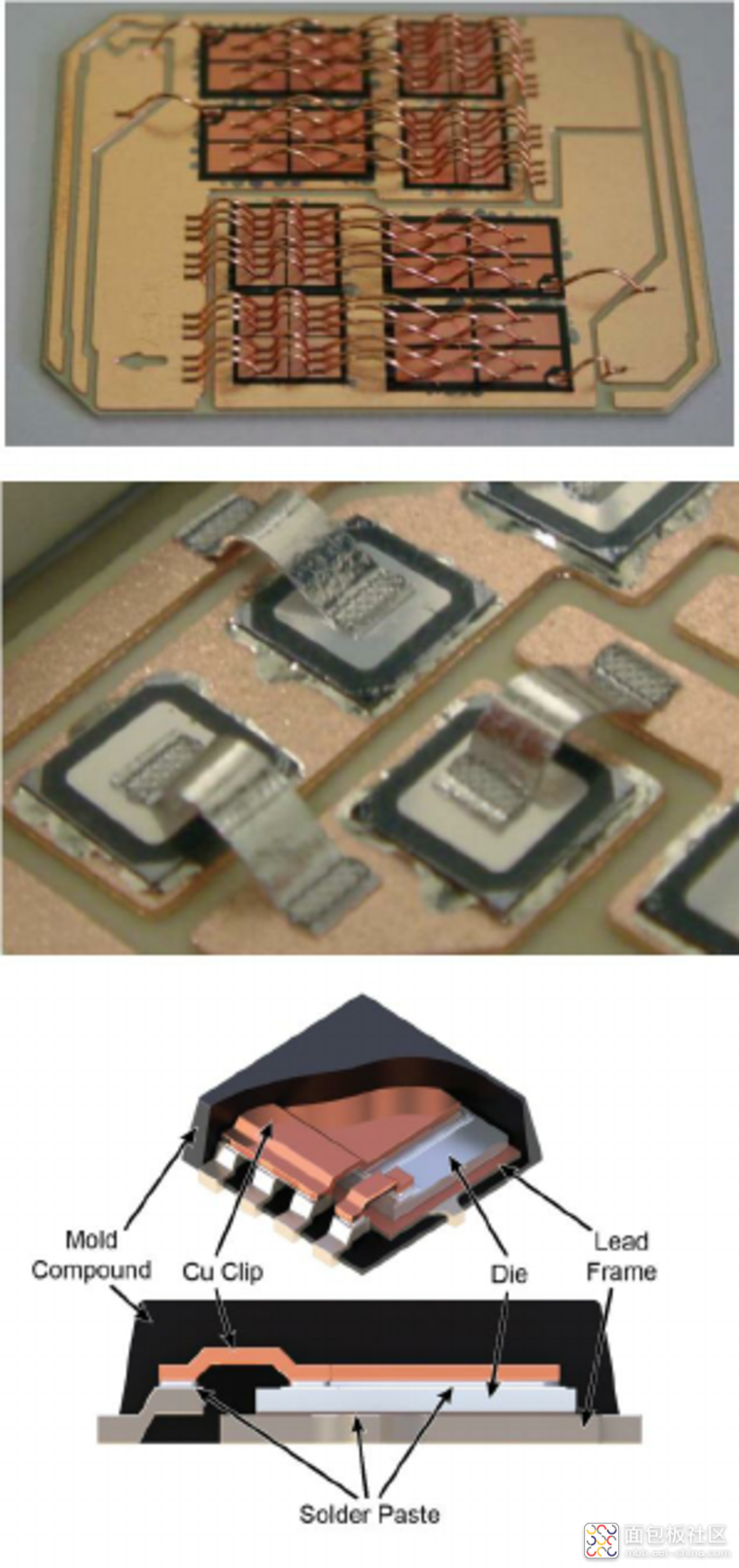

芯片上表面通常都安排有焊垫(Pad),封装时用几十微米直径的金线、铝线或铜线把焊垫和金属框架连起来,这个过程也叫 Wire Bonding,简称WB、打线或引线键合。

功率MOS的上表面通常是S极(面积很大)和G极(面积小)。接触面积越大,电阻就越小。一般的WB工艺实现的是“点接触”,那么可以增加直径,用较粗的铝线来扩大接触点。换用扁平的铝带可以形成“线接触”。终极的解决办法是用一整片铜,让它和金属框架形成上下两片夹子,即铜夹(Copper Clip)。当然焊接工艺的难度也不断增加,尤其是铜夹工艺,需要像 SMT工艺那样去控制锡膏形状、气泡率等等。

(图源自网络,侵删)

3. 源极底置(Source Down)= 漏极顶置

前面两种方式都把器件底部视为功率MOS的主要散热路径,其实PCB的散热能力也是有限的,如何在不改变占PCB面积的前提下继续增加散热面积呢?双面散热封装出现了。和CMOS器件相比,功率器件顶部散热空间较大,所以厂家推出了源极朝下、漏极在上且裸露焊盘的封装,有的还设计为双面带裸露焊盘的双面散热封装。

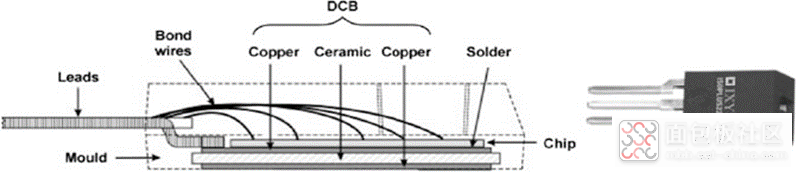

4. 只散热不导电

这种封装采用了DCB(Directed Copper Bonding,直接铜键合)技术,2层铜和一片陶瓷组成“三明治”结构,利用陶瓷绝缘导热的特性实现。代表性的应用其实还是在IGBT和IGBT模块上。

(图源:Semiconductor Power Devices, Springer, 2010)

发热大,需要更好的散热设计,绝不是功率MOSFET独有的“问题”。随着功耗密度的增大,结构、封装对半导体器件性能的影响(限制)越来越明显。当前CMOS工艺半导体器件的功耗密度最高已达到12W/cm^2,超过家用电熨斗的5W/cm^2。从功率MOS双面散热封装,到最先进的晶圆级封装,我认为都是半导体行业在努力突破新的局限。

作者: 电子知识打边炉, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-4061550.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/5

/5

文章评论(0条评论)

登录后参与讨论