专题三:乘法器(二)

在 乘法器(一) 中介绍了采用逻辑实现乘法器的方法,但是在一般情况下,建议使用FPGA中的DSP硬核资源,在项目初期,DSP硬核资源的多少可以作为FPGA芯片选型的标准之一。下面首先看一下DSP硬核资源的使用,以Xlinx FPGA为例,在Kintex-7系列中含有DSP48E1。使用如以下代码:

module multipler_dsp(

input clk,

input rst,

input [15:0] a,

input [15:0] b,

output reg [31:0] p

);

reg [15:0] a_in,b_in;

always@(posedge clk)

if(rst)

begin

a_in<=16'd0;

b_in<=16'd0;

end

else

begin

a_in<=a;

b_in<=b;

end

always@(posedge clk)

if(rst)

p<=32'd0;

else

p<=a * b;

endmodule

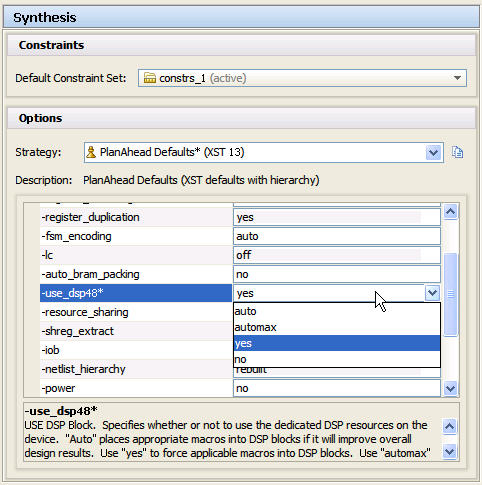

程序中首先对输入a和b寄存,然后采用直接使用乘法符号“*”执行乘法操作,综合器会自动将此操作综合成使用DSP48E1的乘法器,不过为了确保,需要设置综合选项,如图1所示,将-use_dsp48设置成yes;如果设置成no,综合器就会使用LUTs实现这个乘法操作。

图1

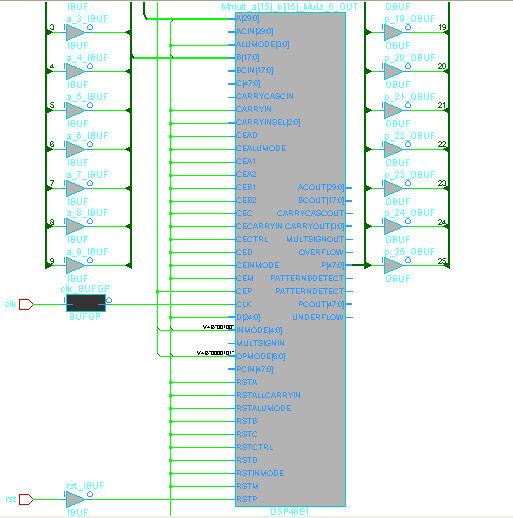

如图2所示为综合结果,综合报告中资源就使用了1个DSP48E1,而Fmax可以达到650.195MHz,相比于使用逻辑实现的乘法器性能上提高了不少,特别是集成在复杂的FPGA设计中,可以跟容易满足时序要求。

图2

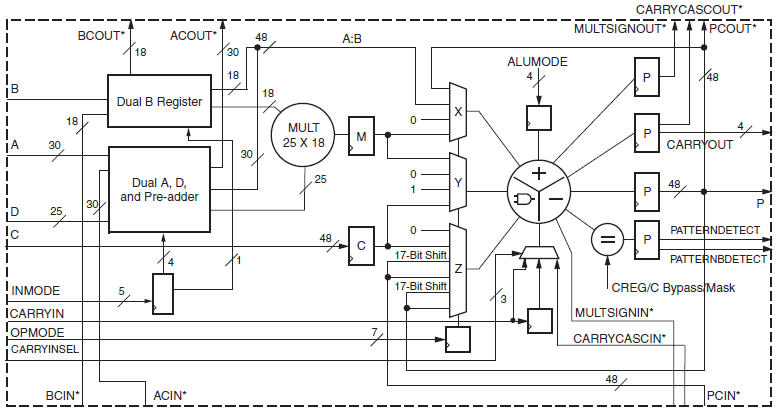

既然提到了DSP48E1,就简单介绍一下吧, 信号去直流方法 就是DSP48E1的一个很好应用。如图3所示为DSP48E1的内部结构,包括输入输出接口、预加器(Pre-adder)、乘法器(MULT)、逻辑运算单元(ALU)和模式检测控制5个部分。输入输出接口最大支持输入A:30-bit、B:18-bit、C:48-bit、D:25-bit和输出P:48-bit;预加器中可实现A和D的加/减操作;乘法器可实现最大18*25的有符号数据的乘法操作;而逻辑运算单元可实现加/减、逻辑控制,一般可用于乘累加;模式检测控制主要通过检测OPMODE输入口,控制DSP48E1内部模块功能。

图3

/4

/4

文章评论(0条评论)

登录后参与讨论